SBAS257 - FEBRUARY 2002

## PDA ANALOG INTERFACE CIRCUIT

### **FEATURES**

- 4-WIRE TOUCH SCREEN INTERFACE

- RATIOMETRIC CONVERSION

- SINGLE 2.7V TO 3.6V SUPPLY

- SERIAL INTERFACE

- INTERNAL DETECTION OF SCREEN TOUCH

- PROGRAMMABLE 8-, 10-, OR 12-BIT RESOLUTION

- PROGRAMMABLE SAMPLING RATES

- DIRECT BATTERY MEASUREMENT (0.5V to 6V)

- ON-CHIP TEMPERATURE MEASUREMENT

- TOUCH-PRESSURE MEASUREMENT

- FULL POWER-DOWN CONTROL

- TSSOP-20 PACKAGE

### **APPLICATIONS**

- PERSONAL DIGITAL ASSISTANTS

- CELLULAR PHONES

- MP3 PLAYERS

### DESCRIPTION

The TSC2000 is a complete PDA analog interface circuit. It contains a complete 12-bit, Analog-to-Digital (A/D) resistive touch screen converter including drivers, the control to measure touch pressure, and an 8-bit Digital-to-Analog (D/A) converter output for LCD contrast control. The TSC2000 interfaces to the host controller through a standard SPI™ serial interface. The TSC2000 offers programmable resolution and sampling rates from 8- to 12-bits and up to 125kHz to accommodate different screen sizes.

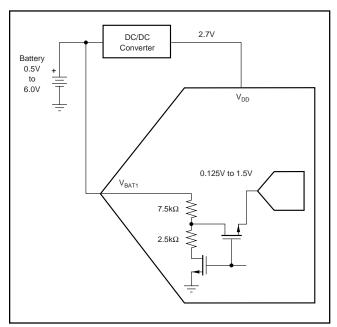

The TSC2000 also offers two battery-measurement inputs, one of which is capable of reading battery voltages up to 6V while operating at only 2.7V. It also has an on-chip temperature sensor capable of reading 0.3°C resolution. The TSC2000 is available in a TSSOP-20 package.

SPI is a registered trademark of Motorola. US Patent No. 624639.

testing of all parameters.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

#### ABSOLUTE MAXIMUM RATINGS(1)

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

|------------------------------------------------------|

| TSSOP Package                                        |

| Power Dissipation $(T_J Max - T_A)/\theta_{JA}$      |

| $\theta_{ m JA}$ Thermal Impedance                   |

| Lead Temperature, Soldering                          |

| Vapor Phase (60s)+215°C                              |

| Infrared (15s)+220°C                                 |

NOTE: (1) Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

# ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

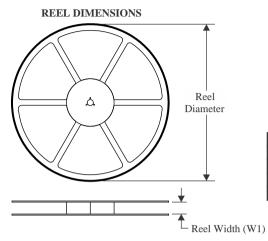

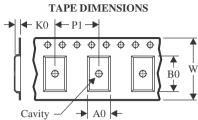

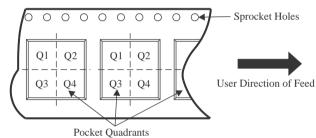

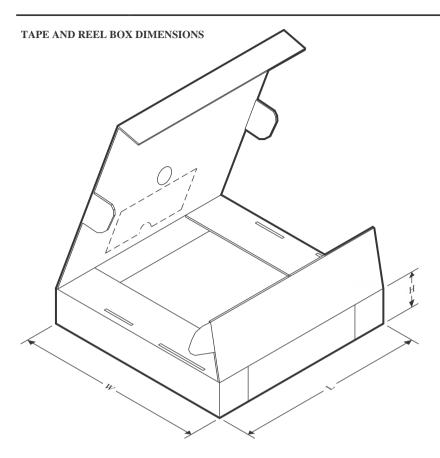

| PRODUCT    | INTEGRAL<br>LINEARITY<br>ERROR (LSB) | PACKAGE-LEAD | PACKAGE<br>DESIGNATOR <sup>(1)</sup> | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER <sup>(2)</sup> | TRANSPORT<br>MEDIA, QUANTITY |

|------------|--------------------------------------|--------------|--------------------------------------|-----------------------------------|--------------------|-----------------------------------|------------------------------|

| TSC2000IPW | ±2                                   | TSSOP-20     | PW                                   | -40°C to +85°C                    | TSC2000I           | TSC2000IPW                        | Rails, 70                    |

| "          | "                                    | "            | "                                    | u .                               | II                 | TSC2000IPWR                       | Tape and Reel, 2000          |

NOTES: (1) For the most current specifications and package information, refer to our web site at www.ti.com. (2) Models labeled with "R" indicates large quantity tape and reel.

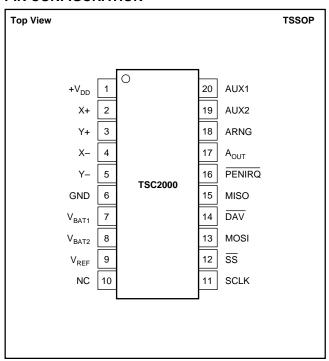

### **PIN CONFIGURATION**

### **PIN DESCRIPTION**

| PIN | NAME              | DESCRIPTION                                                                                                                                                   |

|-----|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | $V_{DD}$          | Power Supply                                                                                                                                                  |

| 2   | X+                | X+ Position Input                                                                                                                                             |

| 3   | Y+                | Y+ Position Input                                                                                                                                             |

| 4   | X–                | X- Position Input                                                                                                                                             |

| 5   | Y-                | Y- Position Input                                                                                                                                             |

| 6   | GND               | Ground                                                                                                                                                        |

| 7   | V <sub>BAT1</sub> | Battery Monitor Input 1                                                                                                                                       |

| 8   | $V_{BAT2}$        | Battery Monitor Input 2                                                                                                                                       |

| 9   | $V_{REF}$         | Voltage Reference Input/Output                                                                                                                                |

| 10  | NC                | No Connection                                                                                                                                                 |

| 11  | SCLK              | Serial Clock Input                                                                                                                                            |

| 12  | SS                | Slave Select Input (Active LOW). Data will not be clocked in to MOSI unless \$\overline{SS}\$ is LOW. When \$\overline{SS}\$ is HIGH, MISO is high impedance. |

| 13  | MOSI              | Serial Data Input. Data is clocked in at SCLK falling edge.                                                                                                   |

| 14  | DAV               | Data Available (Active LOW)                                                                                                                                   |

| 15  | MISO              | Serial Data Output. Data is clocked out at SCLK falling edge. High impedance when SS is HIGH.                                                                 |

| 16  | PENIRQ            | Pen Interrupt                                                                                                                                                 |

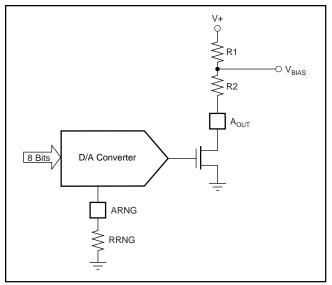

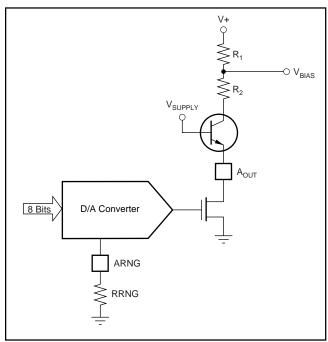

| 17  | A <sub>OUT</sub>  | Analog Output Current from D/A Converter                                                                                                                      |

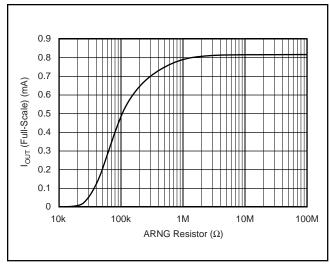

| 18  | ARNG              | D/A Converter Analog Output Range Set                                                                                                                         |

| 19  | AUX2              | Auxiliary A/D Converter Input 2                                                                                                                               |

| 20  | AUX1              | Auxiliary A/D Converter Input 1                                                                                                                               |

## **ELECTRICAL CHARACTERISTICS**

At  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ ,  $+\text{V}_{DD}$  = +2.7V, internal  $\text{V}_{REF}$  = +2.5V, conversion clock = 2MHz, 12-bit mode, unless otherwise noted.

|                                                                                                                                          |                                                                                                     |                                                  | TSC2000IPW              |                                  |                                |

|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------|-------------------------|----------------------------------|--------------------------------|

| PARAMETER                                                                                                                                | CONDITIONS                                                                                          | MIN                                              | TYP                     | MAX                              | UNITS                          |

| AUXILIARY ANALOG INPUT Input Voltage Range Input Capacitance Input Leakage Current                                                       |                                                                                                     | 0                                                | 25<br>±1                | +V <sub>REF</sub>                | V<br>pF<br>μA                  |

| BATTERY MONITOR INPUT Input Voltage Range Input Voltage Range Input Capacitance Input Leakage Current Accuracy                           | VBAT1<br>VBAT2                                                                                      | 0.5<br>0.5                                       | 25<br>±1                | 6.0<br>3.0<br>+3                 | V<br>V<br>pF<br>μA<br>%        |

| TEMPERATURE MEASUREMENT Temperature Range Temperature Resolution Accuracy                                                                |                                                                                                     | -40                                              | 0.3<br>±2               | +85                              | °C<br>°C<br>°C                 |

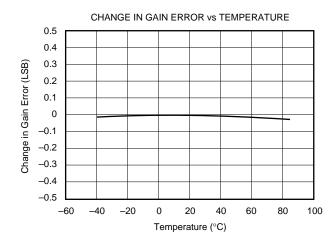

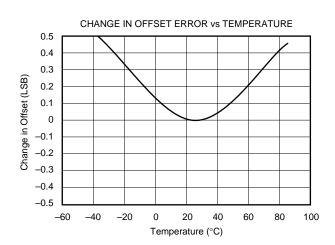

| A/D CONVERTER Resolution No Missing Codes Integral Linearity Offset Error Gain Error Noise Power-Supply Rejection                        | Programmable: 8-, 10-, or 12-Bits<br>12-Bit Resolution<br>Excluding Reference Error                 | 11                                               | 30<br>80                | 12<br>±2<br>±6<br>±6             | Bits Bits LSB LSB LSB MVrms dB |

| D/A CONVERTER Output Current Range Resolution Integral Linearity                                                                         | Set by Resistor from ARNG to GND                                                                    | 650                                              | ±2                      | 8                                | μΑ<br>Bits<br>LSB              |

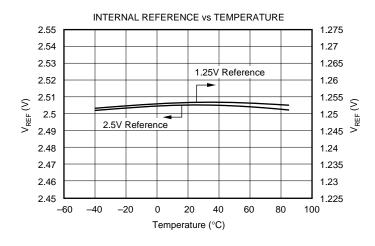

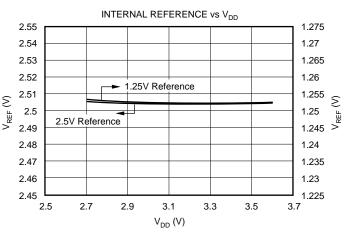

| VOLTAGE REFERENCE Voltage Range Reference Drift External Reference Input Range Current Drain                                             | Internal 2.5V<br>Internal 1.25V<br>External Reference                                               | 2.45<br>1.225<br>1.0                             | 2.5<br>1.25<br>20<br>20 | 2.55<br>1.275<br>V <sub>DD</sub> | V<br>V<br>ppm/°C<br>V<br>μΑ    |

| DIGITAL INPUT/OUTPUT Internal Clock Frequency Logic Family Logic Levels: V <sub>IH</sub> V <sub>IL</sub> V <sub>OH</sub> V <sub>OL</sub> | $I_{IH} = +5\mu A$ $I_{IL} = +5\mu A$ $I_{OH} = 2 \text{ TTL Loads}$ $I_{OL} = 2 \text{ TTL Loads}$ | 0.7V <sub>DD</sub><br>-0.3<br>0.8V <sub>DD</sub> | 8<br>CMOS               | 0.3V <sub>DD</sub>               | MHz<br>V<br>V<br>V             |

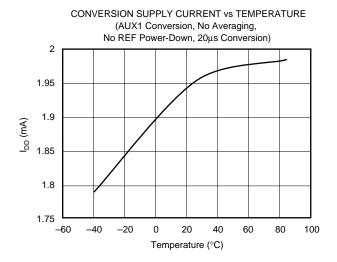

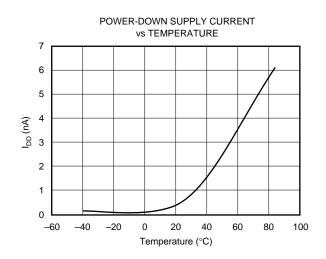

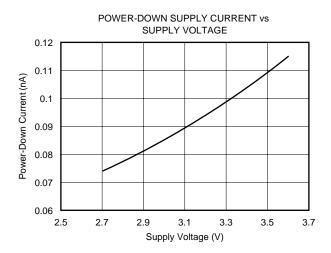

| POWER-SUPPLY REQUIREMENTS Power-Supply Voltage, +V <sub>DD</sub> Quiescent Current                                                       | Specified Performance<br>See Note (1)<br>See Note (2)<br>Power Down                                 | 2.7                                              | 1.25<br>500             | 3.6<br>2.3<br>3                  | V<br>mA<br>μA<br>μA            |

| TEMPERATURE RANGE Specified Performance                                                                                                  |                                                                                                     | -40                                              |                         | +85                              | °C                             |

$NOTES: (1) \ AUX1 \ conversion, \ no \ averaging, \ no \ REF \ power \ down, \ 50\mu s \ conversion. \ (2) \ AUX1 \ conversion, \ no \ averaging, \ external \ reference, \ 50\mu s \ conversion.$

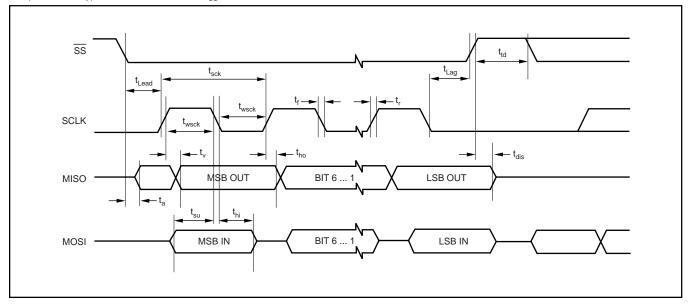

## TIMING CHARACTERISTICS(1)(2)

At  $-40^{\circ}$ C to  $+85^{\circ}$ C,  $+V_{DD}$  = +2.7V,  $V_{REF}$  = +2.5V, unless otherwise noted.

|                                     |                  |     | TSC2000 |     |       |  |  |

|-------------------------------------|------------------|-----|---------|-----|-------|--|--|

| PARAMETER                           | CONDITIONS       | MIN | TYP     | MAX | UNITS |  |  |

| SCLK Period                         | t <sub>sck</sub> | 30  |         |     | ns    |  |  |

| Enable Lead Time                    | $t_Lead$         | 15  |         |     | ns    |  |  |

| Enable Lag Time                     | t <sub>Lag</sub> | 15  |         |     | ns    |  |  |

| Sequential Transfer Delay           | t <sub>td</sub>  | 30  |         |     | ns    |  |  |

| Data Setup Time                     | t <sub>su</sub>  | 10  |         |     | ns    |  |  |

| Data Hold Time (inputs)             | t <sub>hi</sub>  | 10  |         |     | ns    |  |  |

| Data Hold Time (outputs)            | t <sub>ho</sub>  | 0   |         |     | ns    |  |  |

| Slave Access Time                   | t <sub>a</sub>   |     |         | 15  | ns    |  |  |

| Slave D <sub>OUT</sub> Disable Time | t <sub>dis</sub> |     |         | 15  | ns    |  |  |

| DataValid                           | t <sub>v</sub>   |     |         | 10  | ns    |  |  |

| Rise Time                           | t <sub>r</sub>   |     |         | 30  | ns    |  |  |

| Fall Time                           | t <sub>f</sub>   |     |         | 30  | ns    |  |  |

NOTES: (1) All input signals are specified with  $t_r = t_f = 5$ ns (10% to 90% of  $V_{DD}$ ) and timed from a voltage level of  $(V_{IL} + V_{IH})/2$ . (2) See timing diagram below.

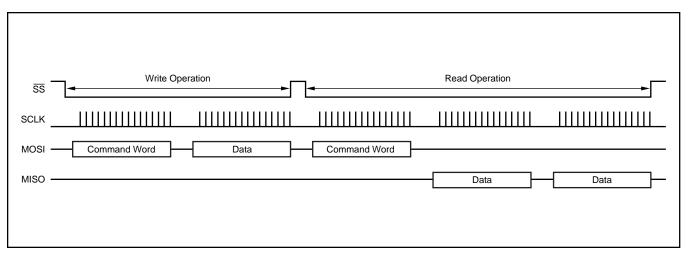

### **TIMING DIAGRAM**

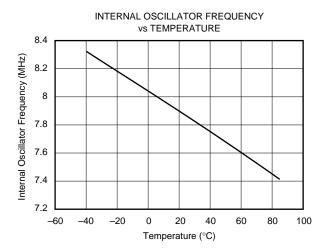

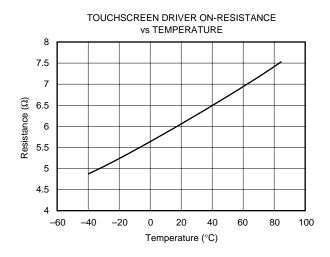

All specifications typical at  $-40^{\circ}$ C to  $+85^{\circ}$ C,  $+V_{DD}$  = +2.7V.

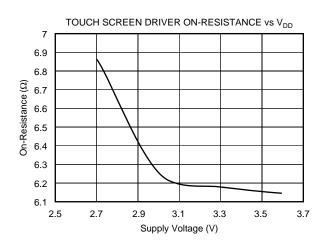

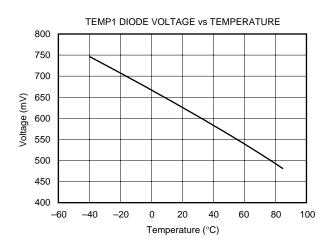

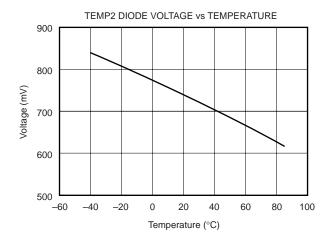

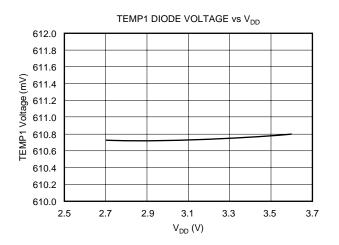

### TYPICAL CHARACTERISTICS

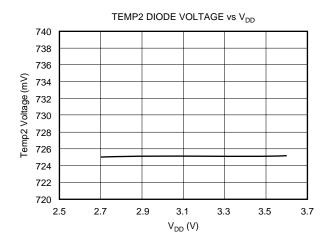

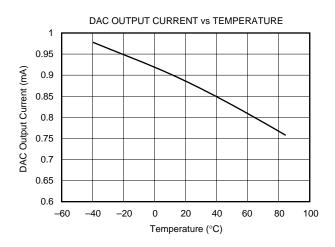

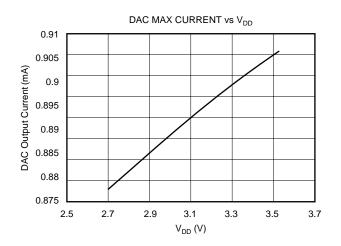

At  $T_A = +25$ °C,  $+V_{DD} = +2.7V$ , conversion clock = 2MHz, 12-bit mode. Internal  $V_{REF} = +2.5V$ , unless otherwise noted.

## **TYPICAL CHARACTERISTICS (Cont.)**

At  $T_A = +25$ °C,  $+V_{DD} = +2.7$ V, conversion clock = 2MHz, 12-bit mode. Internal  $V_{REF} = +2.5$ V, unless otherwise noted.

## **TYPICAL CHARACTERISTICS (Cont.)**

At  $T_A = +25^{\circ}C$ ,  $+V_{DD} = +2.7V$ , conversion clock = 2MHz, 12-bit mode. Internal  $V_{REF} = +2.5V$ , unless otherwise noted.

### **OVERVIEW**

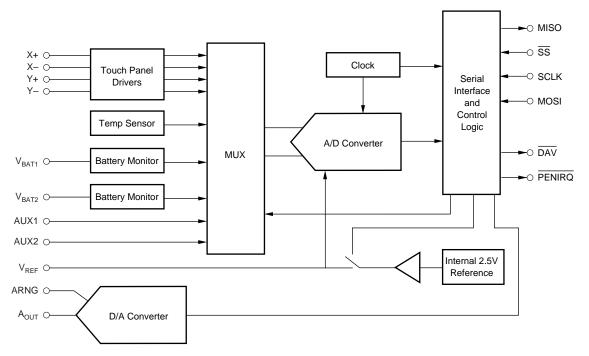

The TSC2000 is an analog interface circuit for human interface devices. A register-based architecture eases integration with microprocessor-based systems through a standard SPI bus. All peripheral functions are controlled through the registers and onboard state machines.

The TSC2000 consists of the following blocks (refer to the block diagram on the front page):

- · Touch Screen Interface

- · Battery Monitors

- · Auxiliary Inputs

- · Temperature Monitor

- · Current Output D/A Converter

Communication to the TSC2000 is via a standard SPI serial interface. This interface requires that the Slave Select signal be driven LOW to communicate with the TSC2000. Data is then shifted into or out of the TSC2000 under control of the host microprocessor, which also provides the serial data clock.

Control of the TSC2000 and its functions is accomplished by writing to different registers in the TSC2000. A simple command protocol is used to address the 16-bit registers. Registers control the operation of the A/D converter and D/A converter.

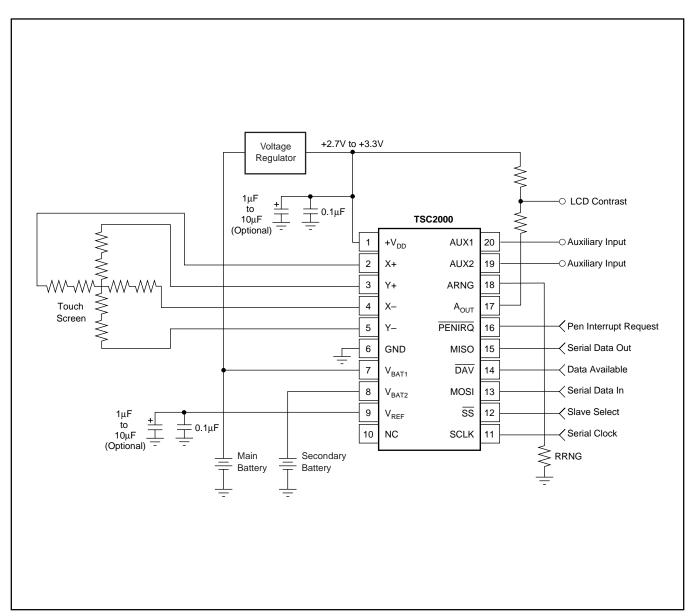

The result of measurements made will be placed in the TSC2000's memory map and may be read by the host at any time. Three signals are available from the TSC2000 to indicate that data is available for the host to read. The  $\overline{\text{DAV}}$  output indicates that an A/D conversion has completed and that data is available. The  $\overline{\text{PENIRQ}}$  output indicates that a touch has been detected on the touch screen. A typical application of the TSC2000 is shown in Figure 1.

FIGURE 1. Typical Circuit Configuration.

#### **OPERATION—TOUCH SCREEN**

A resistive touch screen works by applying a voltage across a resistor network and measuring the change in resistance at a given point on the matrix where a screen is touched by an input stylus, pen, or finger. The change in the resistance ratio marks the location on the touch screen.

The TSC2000 supports the resistive 4-wire configurations (see Figure 1). The circuit determines location in two coordinate pair dimensions, although a third dimension can be added for measuring pressure.

## THE 4-WIRE TOUCH SCREEN COORDINATE PAIR MEASUREMENT

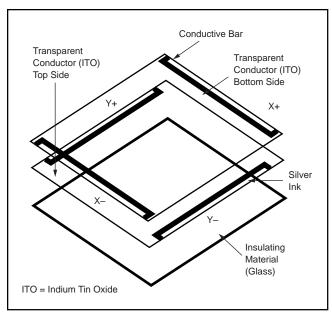

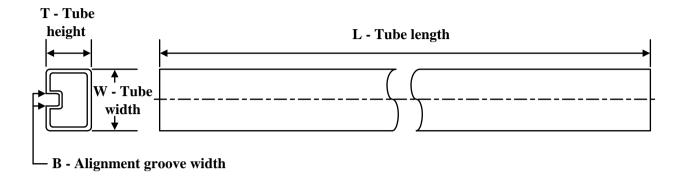

A 4-wire touch screen is constructed as shown in Figure 2. It consists of two transparent resistive layers separated by insulating spacers.

FIGURE 2. 4-Wire Touch Screen Construction.

The 4-wire touch screen panel works by applying a voltage across the vertical or horizontal resistive network. The A/D converter converts the voltage measured at the point the panel is touched. A measurement of the Y-position of the pointing device is made by connecting the X+ input to a data converter chip, turning on the Y+ and Y- drivers, and digitizing the voltage seen at the X+ input. The voltage measured is determined by the voltage divider developed at the point of touch. For this measurement, the horizontal panel resistance in the X+ lead does not affect the conversion due to the high input impedance of the A/D converter. Voltage is then applied to the other axis, and the A/D converter converts the voltage representing the X-position on

Voltage is then applied to the other axis, and the A/D converter converts the voltage representing the X-position on the screen. This provides the X- and Y-coordinates to the associated processor.

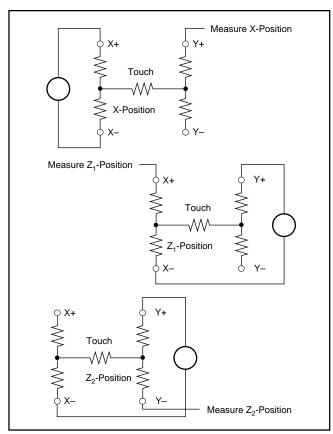

Measuring touch pressure (Z) can also be done with the TSC2000. To determine pen or finger touch, the pressure of the "touch" needs to be determined. Generally, it is not necessary to have very high performance for this test, there-

fore, the 8-bit resolution mode is recommended (however, calculations will be shown with the 12-bit resolution mode). There are several different ways of performing this measurement. The TSC2000 supports two methods. The first method requires knowing the X-plate resistance, measurement of the X-position, and two additional cross panel measurements ( $Z_2$  and  $Z_1$ ) of the touch screen, as seen in Figure 3. Using Equation 1 will calculate the touch resistance:

$$R_{\text{TOUCH}} = R_{\text{X-Plate}} \cdot \frac{\text{X-Position}}{4096} \left( \frac{Z_2}{Z_1} - 1 \right)$$

(1)

FIGURE 3. Pressure Measurement.

The second method requires knowing both the X-plate and Y-plate resistance, measurement of X-position and Y-position, and  $Z_1$ . Using Equation 2 will also calculate the touch resistance:

$$R_{TOUCH} = R_{X-Plate} \cdot \frac{X-Position}{4096} \left(\frac{4096}{Z_1} - 1\right) - R_{Y-Plate} \cdot \frac{Y-Position}{4096}$$

When the touch panel is pressed or touched, and the drivers to the panel are turned on, the voltage across the touch panel will often overshoot and then slowly settle (decay) down to a stable DC value. This is due to mechanical bouncing which is caused by vibration of the top layer sheet of the touch panel when the panel is pressed. This settling time must be accounted for, or else the converted value will be in error. Therefore, a delay must be introduced between the time the driver for a particular measurement is turned on, and the time measurement is made.

In some applications, external capacitors may be required across the touch screen for filtering noise picked up by the touch screen; i.e., noise generated by the LCD panel or back-light circuitry. The value of these capacitors will provide a low-pass filter to reduce the noise, but will cause an additional settling time requirement when the panel is touched. Several solutions to this problem are available in the TSC2000. A programmable delay time is available which sets the delay between turning the drivers on and making a conversion. This is referred to as the Panel Voltage Stabilization time, and is used in some of the modes available in the TSC2000. In other modes, the TSC2000 can be commanded to turn on the drivers only without performing a conversion. Time can then be allowed before a conversion is started.

The TSC2000 touch screen interface can measure position (X and Y) and pressure (Z). Determination of these coordinates is possible under three different modes of the A/D converter: conversion controlled by the TSC2000, initiated by detection of a touch; conversion controlled by the TSC2000, initiated by the host responding to the  $\overline{\text{PENIRQ}}$  signal; or conversion completely controlled by the host processor.

### A/D CONVERTER

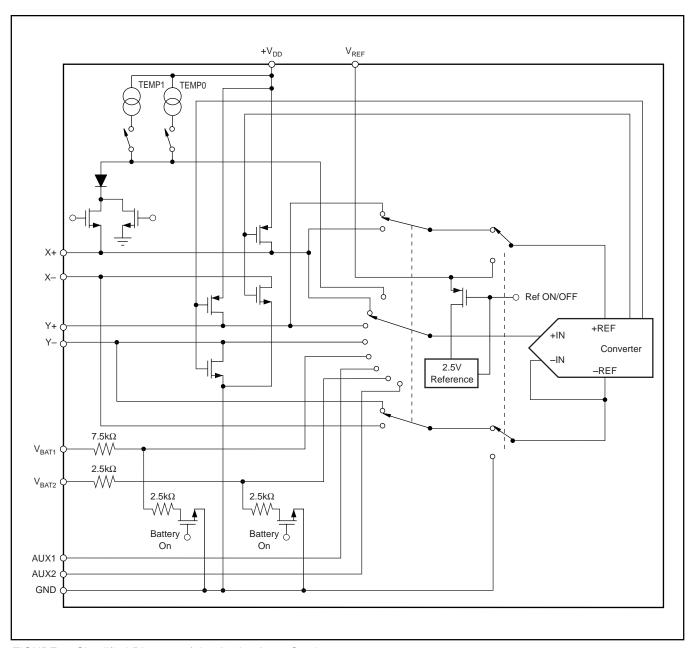

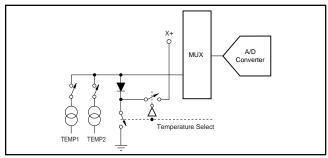

The analog inputs of the TSC2000 are shown in Figure 4. The analog inputs (X, Y, and Z touch panel coordinates, battery voltage monitors, chip temperature, and auxiliary inputs) are provided via a multiplexer to the Successive Approximation Register (SAR) A/D converter. The A/D converter architecture is based on capacitive redistribution architecture which inherently includes a sample-and-hold function.

FIGURE 4. Simplified Diagram of the Analog Input Section.

A unique configuration of low on-resistance switches allows an unselected A/D converter input channel to provide power and an accompanying pin to provide ground for driving the touch panel. By maintaining a differential input to the converter and a differential reference input architecture, it is possible to negate errors caused by the driver switch on-resistances.

The A/D converter is controlled by an A/D Converter Control Register. Several modes of operation are possible, depending upon the bits set in the control register. Channel selection, scan operation, averaging, resolution, and conversion rate may all be programmed through this register. These modes are outlined in the sections below for each type of analog input. The results of conversions made are stored in the appropriate result register.

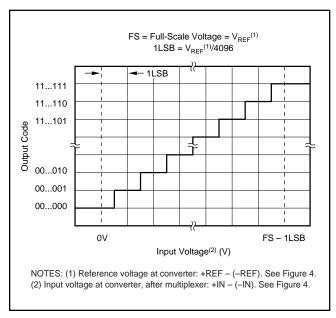

#### **Data Format**

The TSC2000 output data is in Straight Binary format, as shown in Figure 5. This figure shows the ideal output code for the given input voltage and does not include the effects of offset, gain, or noise.

FIGURE 5. Ideal Input Voltages and Output Codes.

#### Reference

The TSC2000 has an internal voltage reference that can be set to 1.25V or 2.5V, through the Reference Control Register.

The internal reference voltage is only used in the single-ended mode for battery monitoring, temperature measurement, and for utilizing the auxiliary inputs. Optimal touch screen performance is achieved when using a ratiometric conversion, thus all touch screen measurements are done automatically in the differential mode. An external reference can also be applied to the  $V_{REF}$  pin, and the internal reference can be turned off.

### Variable Resolution

The TSC2000 provides three different resolutions for the A/D converter: 8-, 10-, or 12-bits. Lower resolutions are often practical for measurements such as touch pressure. Perform-

ing the conversions at lower resolutions reduces the amount of time it takes for the A/D converter to complete its conversion process, which lowers power consumption.

#### **Conversion Clock and Conversion Time**

The TSC2000 contains an internal 8MHz clock, which is used to drive the state machines inside the device that perform the many functions of the part. This clock is divided down to provide a clock to run the A/D converter. The division ratio for this clock is set in the A/D Converter Control Register. The ability to change the conversion clock rate allows the user to choose the optimal value for resolution, speed, and power. If the 8MHz clock is used directly, the A/D converter is limited to 8-bit resolution; using higher resolutions at this speed will not result in accurate conversions. Using a 4MHz conversion clock is suitable for 10-bit resolution; 12-bit resolution requires that the conversion clock run at 1MHz or 2MHz.

Regardless of the conversion clock speed, the internal clock will run nominally at 8MHz. The conversion time of the TSC2000 is dependent upon several functions. While the conversion clock speed plays an important role in the time it takes for a conversion to complete, a certain number of internal clock cycles is needed for proper sampling of the signal. Moreover, additional times, such as the Panel Voltage Stabilization time, can add significantly to the time it takes to perform a conversion. Conversion time can vary depending upon the mode in which the TSC2000 is used. Throughout this data sheet, internal and conversion clock cycles will be used to describe the times that many functions take. In considering the total system design, these times must be taken into account by the user.

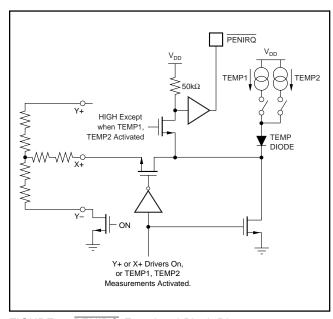

### **Touch Detect**

The pen interrupt (PENIRQ) output function is detailed in Figure 6. While in the power-down mode, the Y- driver is ON and connected to GND and the PENIRQ output is connected to the X+ input. When the panel is touched, the X+ input is

FIGURE 6. PENIRQ Functional Block Diagram.

pulled to ground through the touch screen and PENIRQ output goes LOW due to the current path through the panel to GND, initiating an interrupt to the processor. During the measurement cycles for the X- and Y-positions, the X+ input will be disconnected from the PENIRQ pull-down transistor to eliminate any leakage current from the pull-up resistor to flow through the touch screen, thus causing no errors.

In modes where the TSC2000 needs to detect if the screen is still touched (for example, when doing a  $\overline{\text{PENIRQ}}\text{-initiated}$  X, Y, and Z conversion), the TSC2000 must reset the drivers so that the  $50\text{k}\Omega$  resistor is connected again. Due to the high value of this pull-up resistor, any capacitance on the touch screen inputs will cause a long delay time, and may prevent the detection from occurring correctly. To prevent this, the TSC2000 has a circuit which allows any screen capacitance to be "precharged", so that the pull-up resistor doesn't have to be the only source for the charging current. The time allowed for this precharge, as well as the time needed to sense if the screen is still touched, can be set in the Configuration Control register.

This illustrates the need to use the minimum capacitor values possible on the touch screen inputs. These capacitors may be needed to reduce noise, but too large a value will increase the needed precharge and sense times, as well as panel voltage stabilization time.

### DIGITAL INTERFACE

The TSC2000 communicates through a standard SPI bus. The SPI allows full-duplex, synchronous, serial communication between a host processor (the master) and peripheral devices (slaves). The SPI master generates the synchronizing clock and initiates transmissions. The SPI slave devices depend on a master to start and synchronize transmissions.

A transmission begins when initiated by a master SPI. The byte from the master SPI begins shifting in on the slave MOSI pin under the control of the master serial clock. As the byte shifts in on the MOSI pin, a byte shifts out on the MISO pin to the master shift register.

The idle state of the serial clock for the TSC2000 is LOW, which corresponds to a clock polarity setting of 0 (typical microprocessor SPI control bit CPOL = 0). The TSC2000 interface is designed so that with a clock phase bit setting of 1 (typical microprocessor SPI control bit CPHA = 1), the master begins driving its MOSI pin and the slave begins driving its MISO pin on the first serial clock edge. The  $\overline{SS}$  pin should idle HIGH between transmissions. The TSC2000 will only interpret command words which are transmitted after the falling edge of  $\overline{SS}$ .

#### TSC2000 COMMUNICATION PROTOCOL

The TSC2000 is entirely controlled by registers. Reading and writing these registers is accomplished by the use of a 16-bit command, which is sent prior to the data for that register. The command is constructed as shown in Table I.

The command word begins with a  $R/\overline{W}$  bit, which specifies the direction of data flow on the serial bus. The following four bits specify the page of memory this command is directed to, as shown in Table II. The next six bits specify the register address on that page of memory to which the data is directed. The last five bits are reserved for future use.

| PG3 | PG2 | PG1 | PG0        | PAGE ADDRESSED |  |  |  |  |

|-----|-----|-----|------------|----------------|--|--|--|--|

| 0   | 0   | 0   | 0          | 0              |  |  |  |  |

| 0   | 0   | 0   | 1          | 1              |  |  |  |  |

| 0   | 0   | 1   | 0 Reserved |                |  |  |  |  |

| 0   | 0   | 1   | 1          | Reserved       |  |  |  |  |

| 0   | 1   | 0   | 0          | Reserved       |  |  |  |  |

| 0   | 1   | 0   | 1          | Reserved       |  |  |  |  |

| 0   | 1   | 1   | 0          | Reserved       |  |  |  |  |

| 0   | 1   | 1   | 1          | Reserved       |  |  |  |  |

| 1   | 0   | 0   | 0          | Reserved       |  |  |  |  |

| 1   | 0   | 0   | 1          | Reserved       |  |  |  |  |

| 1   | 0   | 1   | 0          | Reserved       |  |  |  |  |

| 1   | 0   | 1   | 1          | Reserved       |  |  |  |  |

| 1   | 1   | 0   | 0          | Reserved       |  |  |  |  |

| 1   | 1   | 0   | 1          | Reserved       |  |  |  |  |

| 1   | 1   | 1   | 0          | Reserved       |  |  |  |  |

| 1   | 1   | 1   | 1          | Reserved       |  |  |  |  |

TABLE II. Page Addressing.

| MSB<br>BIT 15 | BIT 14 | BIT 13 | BIT 12 | BIT 11 | BIT 10 | BIT 9 | BIT 8 | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | LSB<br>BIT 0 |

|---------------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|--------------|

| R/W           | PG3    | PG2    | PG1    | PG0    | ADDR5  | ADDR4 | ADDR3 | ADDR2 | ADDR1 | ADDR0 | Х     | Х     | Х     | Х     | Х            |

TABLE I. TSC2000 Command Word.

To read all the first page of memory, for example, the host processor must send the TSC2000 the command  $8000_{\rm H}$ —this specifies a read operation beginning at Page 0, Address 0. The processor can then start clocking data out of the TSC2000. The TSC2000 will automatically increment its address pointer to the end of the page; if the host processor continues clocking data out past the end of a page, the TSC2000 will simply send back the value FFFF<sub>H</sub>.

Likewise, writing to Page 1 of memory would consist of the processor writing the command  $0800_{\rm H}$ , which would specify a write operation, with PG0 set to 1, and all the ADDR bits set to 0. This would result in the address pointer pointing at the first location in memory on Page 1. See the TSC2000 Memory Map section for details of register locations. Figure 7 shows an example of a complete data transaction between the host processor and the TSC2000.

### **TSC2000 MEMORY MAP**

The TSC2000 has several 16-bit registers which allow control of the device as well as providing a location for results from the TSC2000 to be stored until read by the host microprocessor. These registers are separated into two pages of memory in the TSC2000: a Data page (Page 0) and a Control page (Page 1). The memory map is shown in Table III.

| PAGE 0: DAT | A REGISTERS    | PAGE 1: CONTR | OL REGISTERS |

|-------------|----------------|---------------|--------------|

| ADDR        | REGISTER       | ADDR          | REGISTER     |

| 00          | X              | 00            | ADC          |

| 01          | Υ              | 01            | Reserved     |

| 02          | Z <sub>1</sub> | 02            | DACCTL       |

| 03          | $Z_2$          | 03            | REF          |

| 04          | Reserved       | 04            | RESET        |

| 05          | BAT1           | 05            | CONFIG       |

| 06          | BAT2           | 06            | Reserved     |

| 07          | AUX1           | 07            | Reserved     |

| 08          | AUX2           | 08            | Reserved     |

| 09          | TEMP1          | 09            | Reserved     |

| 0A          | TEMP2          | 0A            | Reserved     |

| 0B          | DAC            | 0B            | Reserved     |

| 0C          | Reserved       | 0C            | Reserved     |

| 0D          | Reserved       | 0D            | Reserved     |

| 0E          | Reserved       | 0E            | Reserved     |

| 0F          | Reserved       | 0F            | Reserved     |

| 10          | ZERO           | 10            | Reserved     |

| 11          | Reserved       | 11            | Reserved     |

| 12          | Reserved       | 12            | Reserved     |

| 13          | Reserved       | 13            | Reserved     |

| 14          | Reserved       | 14            | Reserved     |

| 15          | Reserved       | 15            | Reserved     |

| 16          | Reserved       | 16            | Reserved     |

| 17          | Reserved       | 17            | Reserved     |

| 18          | Reserved       | 18            | Reserved     |

| 19          | Reserved       | 19            | Reserved     |

| 1A          | Reserved       | 1A            | Reserved     |

| 1B          | Reserved       | 1B            | Reserved     |

| 1C          | Reserved       | 1C            | Reserved     |

| 1D          | Reserved       | 1D            | Reserved     |

| 1E          | Reserved       | 1E            | Reserved     |

| 1F          | Reserved       | 1F            | Reserved     |

TABLE III. TSC2000 Memory Map.

FIGURE 7. Write and Read Operation of TSC2000 Interface.

### **TSC2000 CONTROL REGISTERS**

This section will describe each of the registers that were shown in the memory map of Table III. The registers are grouped according to the function they control. Note that in

the TSC2000, bits in control registers may refer to slightly different functions depending upon if you are reading the register or writing to it. A summary of all registers and bit locations is shown in Table IV.

|       |               |                      | l   |        |     |        |            |            |          |          |          |          |          |          |          |          |          |          | RESET          |

|-------|---------------|----------------------|-----|--------|-----|--------|------------|------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------------|

| PAGE  | ADDR<br>(HEX) | REGISTER<br>NAME     | D15 | D14    | D13 | D12    | D11        | D10        | D9       | D8       | D7       | D6       | D5       | D4       | D3       | D2       | D1       | D0       | VALUE<br>(HEX) |

| 0     | 00            | Х                    | 0   | 0      | 0   | 0      | R11        | R10        | R9       | R8       | R7       | R6       | R5       | R4       | R3       | R2       | R1       | R0       | 0000           |

| 0     | 01            | Y                    | 0   | 0      | 0   | 0      | R11        | R10        | R9       | R8       | R7       | R6       | R5       | R4       | R3       | R2       | R1       | R0       | 0000           |

| 0     | 02            | $Z_1$                | 0   | 0      | 0   | 0      | R11        | R10        | R9       | R8       | R7       | R6       | R5       | R4       | R3       | R2       | R1       | R0       | 0000           |

| 0     | 03            | Z <sub>2</sub>       | 0   | 0      | 0   | 0      | R11        | R10        | R9       | R8       | R7       | R6       | R5       | R4       | R3       | R2       | R1       | R0       | 0000           |

| 0     | 04            | Reserved             | 0   | 0      | 0   | 0      | 0          | 0          | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0000           |

| 0     | 05<br>06      | BAT1<br>BAT2         | 0   | 0      | 0   | 0      | R11<br>R11 | R10<br>R10 | R9<br>R9 | R8<br>R8 | R7<br>R7 | R6<br>R6 | R5<br>R5 | R4<br>R4 | R3<br>R3 | R2<br>R2 | R1<br>R1 | R0<br>R0 | 0000<br>0000   |

| 0     | 07            | AUX1                 | 0   | 0      | 0   | 0      | R11        | R10        | R9       | R8       | R7       | R6       | R5       | R4       | R3       | R2       | R1       | R0       | 0000           |

| 0     | 08            | AUX2                 | 0   | 0      | 0   | 0      | R11        | R10        | R9       | R8       | R7       | R6       | R5       | R4       | R3       | R2       | R1       | R0       | 0000           |

| 0     | 09            | TEMP1                | 0   | 0      | 0   | 0      | R11        | R10        | R9       | R8       | R7       | R6       | R5       | R4       | R3       | R2       | R1       | R0       | 0000           |

| 0     | 0A            | TEMP2                | 0   | 0      | 0   | 0      | R11        | R10        | R9       | R8       | R7       | R6       | R5       | R4       | R3       | R2       | R1       | R0       | 0000           |

| 0     | 0B            | DAC                  | X   | X      | X   | X      | X          | X          | X        | X        | D7       | D6       | D5       | D4       | D3       | D2       | D1       | D0       | 007F           |

| 0     | OC<br>OD      | Reserved<br>Reserved | 1 1 | 1      | 1 1 | 1      | 1          | 1          | 1<br>1   | 1 1      | 1        | 1 1      | 1 1      | 1 1      | 1 1      | 1 1      | 1 1      | 1        | FFFF<br>FFFF   |

| 0     | 0E            | Reserved             | 1   | 1 1    |     | 1      | 1          | 1          | 1        | 1 1      | 1 1      |          |          |          | 1 1      | 1 1      | 1 1      | 1 1      | FFFF           |

| 0     | 0F            | Reserved             | 1   | 1      | 1   | 1      | 1          | 1          | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | FFFF           |

| 0     | 10            | ZERO                 | 0   | 0      | 0   | 0      | 0          | 0          | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0000           |

| 0     | 11            | Reserved             | 1   | 1      | 1   | 1      | 1          | 1          | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | FFFF           |

| 0     | 12            | Reserved             | 1   | 1      | 1   | 1      | 1          | 1          | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | FFFF           |

| 0     | 13            | Reserved             | 1 1 | 1      | 1   | 1      | 1          | 1          | 1        | 1        | 1        | 1        | 1 1      | 1        | 1        | 1        | 1        | 1 1      | FFFF           |

| 0     | 14<br>15      | Reserved<br>Reserved | 1 1 | 1 1    | 1 1 | 1      | 1          | 1 1        | 1<br>1   | 1<br>  1 | 1        | 1 1      | 1 1      | 1 1      | 1 1      | 1 1      | 1 1      | 1        | FFFF<br>FFFF   |

| 0     | 16            | Reserved             | 1   |        |     | 1      | 1          |            | 1        |          |          | l        |          |          | 1        |          |          |          | FFFF           |

| 0     | 17            | Reserved             | 1   | 1      | 1   | 1      | 1          | 1          | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | FFFF           |

| 0     | 18            | Reserved             | 1   | 1      | 1   | 1      | 1          | 1          | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | FFFF           |

| 0     | 19            | Reserved             | 1   | 1      | 1   | 1      | 1          | 1          | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | FFFF           |

| 0     | 1A            | Reserved             | 1   | 1      | 1   | 1      | 1          | 1          | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | FFFF           |

| 0     | 1B            | Reserved             | 1   | 1      | 1 1 | 1      | 1          | 1          | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | FFFF           |

| 0     | 1C<br>1D      | Reserved<br>Reserved | 1 1 | 1 1    | 1 1 | 1      | 1          | 1 1        | 1<br>1   | 1 1      | 1        | 1 1      | 1 1      | 1 1      | 1 1      | 1 1      | 1 1      | 1        | FFFF<br>FFFF   |

| 0     | 1E            | Reserved             | 1   |        |     | 1      | 1          |            | 1        |          |          |          |          |          | 1        |          |          |          | FFFF           |

| ő     | 1F            | Reserved             | 1   | 1      | 1   | 1      | 1          | 1          | 1        | 1        | 1        | 1        |          | 1        | 1        | 1        | 1        | 1        | FFFF           |

| 1     | 00            | ADC                  | PSM | STS    | AD3 | AD2    | AD1        | AD0        | RS1      | RS0      | AV1      | AV0      | CL1      | CL0      | PV2      | PV1      | PV0      | х        | 4000           |

| 1     | 01            | Reserved             | 0   | 1      | 0   | 0      | 0          | 0          | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 4000           |

| 1     | 02            | DACCTL               | DPD | 0      | 0   | 0      | 0          | 0          | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 8000           |

| 1     | 03            | REF                  | X   | X<br>0 | X   | X<br>1 | X          | X          | X<br>1   | X        | X        | X        | X        | INT      | DL1      | DL0      | PND      | RFV      | 0002           |

| 1     | 04<br>05      | RESET<br>CONFIG      | 1 1 | 1      | 1 1 | 1      | 1          | 0          | 1        | 1        | 1 X      | 1 X      | PR2      | X<br>PR1 | X<br>PR0 | X<br>SN2 | X<br>SN1 | X<br>SN0 | FFFF<br>FFC0   |

| 1 1   | 06            | Reserved             | 1   | 1      |     | 1      | 1          | 1          | 1        |          | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | FFFF           |

| 1     | 07            | Reserved             | 1   | 1      | 1   | 1      | 1          | 1          | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | FFFF           |

| 1     | 08            | Reserved             | 1   | 1      | 1   | 1      | 1          | 1          | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | FFFF           |

| 1     | 09            | Reserved             | 1   | 1      | 1   | 1      | 1          | 1          | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | FFFF           |

| 1     | OA            | Reserved             | 1   | 1      | 1 1 | 1      | 1          | 1          | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | FFFF           |

| 1     | 0B<br>0C      | Reserved<br>Reserved | 1 1 | 1 1    | 1 1 | 1      | 1          | 1          | 1        | 1 1      | 1        | 1 1      | 1 1      | 1 1      | 1 1      | 1 1      | 1 1      | 1 1      | FFFF<br>FFFF   |

| 1     | 0D            | Reserved             | 1   | 1 1    | 1 1 | 1      | 1          | 1          | 1        | 1 1      | '        |          |          | 1        | 1 1      | 1 1      | 1 1      | 1 1      | FFFF           |

| 1     | 0E            | Reserved             | 1   | 1      | 1   | 1      | 1          | 1          | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | FFFF           |

| 1     | 0F            | Reserved             | 1   | 1      | 1   | 1      | 1          | 1          | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | FFFF           |

| 1     | 10            | Reserved             | 0   | 0      | 0   | 0      | 0          | 0          | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0000           |

| 1     | 11            | Reserved             | 1   | 1      | 1   | 1      | 1          | 1          | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | FFFF           |

| 1     | 12<br>13      | Reserved<br>Reserved | 1 1 | 1      | 1 1 | 1      | 1<br>1     | 1          | 1<br>1   | 1        | 1 1      | 1 1      | 1 1      | 1 1      | 1 1      | 1        | 1 1      | 1        | FFFF<br>FFFF   |

| 1     | 14            | Reserved             | 1   | 1 1    | 1 1 | 1      | 1          | 1          | 1        | 1 1      | 1 1      |          |          | 1        | 1 1      | 1 1      | 1 1      | 1 1      | FFFF           |

| 1     | 15            | Reserved             | 1   | 1      | 1   | 1      | 1          | 1          | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | FFFF           |

| 1     | 16            | Reserved             | 1   | 1      | 1   | 1      | 1          | 1          | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | FFFF           |

| 1     | 17            | Reserved             | 1   | 1      | 1   | 1      | 1          | 1          | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | FFFF           |

| 1     | 18            | Reserved             | 1   | 1      | 1   | 1      | 1          | 1          | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | FFFF           |

| 1     | 19<br>1 A     | Reserved             | 1   | 1      | 1   | 1      | 1          | 1          | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | FFFF           |

| 1     | 1A<br>1B      | Reserved<br>Reserved | 1 1 | 1      | 1 1 | 1      | 1<br>1     | 1          | 1<br>1   | 1        | 1 1      | 1 1      | 1 1      | 1 1      | 1 1      | 1        | 1 1      | 1        | FFFF<br>FFFF   |

| 1     | 1C            | Reserved             | 1   | 1 1    | 1 1 | 1      | 1          | 1          | 1        | 1 1      | '        |          |          | 1        | 1 1      | 1 1      | 1 1      | 1 1      | FFFF           |

| 1     | 1D            | Reserved             | 1   | 1      | 1   | 1      | 1          | 1          | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | FFFF           |

| 1     | 1E            | Reserved             | 1   | 1      | 1   | 1      | 1          | 1          | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | FFFF           |

| 1     | 1F            | Reserved             | 1   | 1      | 1   | 1      | 1          | 1          | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | FFFF           |

| NOTE: | X = Don       | i't Care.            |     |        |     |        |            |            |          |          |          |          |          |          |          |          |          |          |                |

TABLE IV. Register Summary for TSC2000.

## TSC2000 A/D CONVERTER CONTROL REGISTER (PAGE 1, ADDRESS 00<sub>H</sub>)

The A/D converter in the TSC2000 is shared between all the different functions. A control register determines which input is selected, as well as other options. The result of the conversion is placed in one of the result registers in Page 0 of memory, depending upon the function selected.

The A/D Converter Control Register controls several aspects of the A/D converter. The register is formatted as shown in Table VI.

**Bit 15: PSM**—Pen Status/Control Mode. Reading this bit allows the host to determine if the screen is touched. Writing to this bit determines the mode used to read coordinates: host controlled, or under control of the TSC2000 responding to a screen touch. When reading, the PENSTS bit indicates if the pen is down or not. When writing to this register, this bit determines if the TSC2000 controls the reading of coordinates, or if the coordinate conversions are host-controlled. The default state is host-controlled conversions (0).

|            | PSM   |                                   |  |  |  |  |  |  |

|------------|-------|-----------------------------------|--|--|--|--|--|--|

| READ/WRITE | VALUE | DESCRIPTION                       |  |  |  |  |  |  |

| Read       | 0     | No Screen Touch Detected          |  |  |  |  |  |  |

| Read       | 1     | Screen Touch Detected             |  |  |  |  |  |  |

| Write      | 0     | Conversions Controlled by Host    |  |  |  |  |  |  |

| Write      | 1     | Conversions Controlled by TSC2000 |  |  |  |  |  |  |

TABLE V. PSM Bit Operation.

**Bit 14: STS**—A/D Converter Status. When reading this bit indicates if the converter is busy, or if conversions are complete and data is available. Writing a 0 to this bit will cause touch screen scans to continue until either the pen is

lifted or the process is stopped. Continuous scans or conversions can be stopped by writing a 1 to this bit. This will immediately halt a conversion (even if the pen is still down) and cause the A/D converter to power down. The default state is continuous conversions, but if this bit is read after a reset or power-up, it will read 1.

|                              | STS |                                             |  |  |  |  |  |  |

|------------------------------|-----|---------------------------------------------|--|--|--|--|--|--|

| READ/WRITE VALUE DESCRIPTION |     |                                             |  |  |  |  |  |  |

| Read                         | 0   | Converter is Busy                           |  |  |  |  |  |  |

| Read                         | 1   | Conversions are Complete, Data is Available |  |  |  |  |  |  |

| Write                        | 0   | Normal Operation                            |  |  |  |  |  |  |

| Write                        | 1   | Stop Conversion and Power Down              |  |  |  |  |  |  |

TABLE VII. STS Bit Operation.

**Bits [13:10]:** AD3-AD0—A/D Converter Function Select Bits. These bits control which input is to be converted, and what mode the converter is placed in. These bits are the same whether reading or writing. A complete listing of how these bits are used is shown in Table VIII.

**Bits[9:8]: RS1, RS0**—Resolution Control. The A/D converter resolution is specified with these bits. A description of these bits is shown in Table IX. These bits are the same whether reading or writing.

| RS1 | RS0 | FUNCTION                                       |

|-----|-----|------------------------------------------------|

| 0   | 0   | 12-Bit Resolution. Power up and reset default. |

| 0   | 1   | 8-Bit Resolution                               |

| 1   | 0   | 10-Bit Resolution                              |

| 1   | 1   | 12-Bit Resolution                              |

TABLE IX. A/D Converter Resolution Control.

| MSB<br>BIT 15 | BIT 14 | BIT 13 | BIT 12 | BIT 11 | BIT 10 | BIT 9 | BIT 8 | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | LSB<br>BIT 0 |

|---------------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|--------------|

| PSM           | STS    | AD3    | AD2    | AD1    | AD0    | RS1   | RS0   | AV1   | AV0   | CL1   | CL0   | PV2   | PV1   | PV0   | Х            |

TABLE VI. A/D Converter Control Register.

| A/D3 | A/D2 | A/D1 | A/D0 | FUNCTION                                                                                                                      |

|------|------|------|------|-------------------------------------------------------------------------------------------------------------------------------|

| 0    | 0    | 0    | 0    | Invalid. No registers will be updated. This is the default state after a reset.                                               |

| 0    | 0    | 0    | 1    | Touch screen scan function: X and Y coordinates converted and the results returned to X and Y data registers.                 |

|      |      |      |      | Scan continues until either the pen is lifted or a stop bit is sent.                                                          |

| 0    | 0    | 1    | 0    | Touch screen scan function: X, Y, $Z_1$ , and $Z_2$ coordinates converted and the results returned to X, Y, $Z_1$ , and $Z_2$ |

|      |      |      |      | data registers. Scan continues until either the pen is lifted or a stop bit is sent.                                          |

| 0    | 0    | 1    | 1    | Touch screen scan function: X coordinate converted and the results returned to X data register.                               |

| 0    | 1    | 0    | 0    | Touch screen scan function: Y coordinate converted and the results returned to Y data register.                               |

| 0    | 1    | 0    | 1    | Touch screen scan function: $Z_1$ and $Z_2$ coordinates converted and the results returned to $Z_1$ and $Z_2$ data registers. |

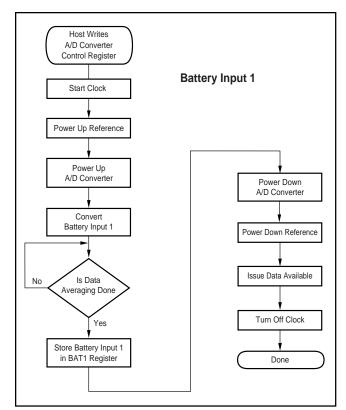

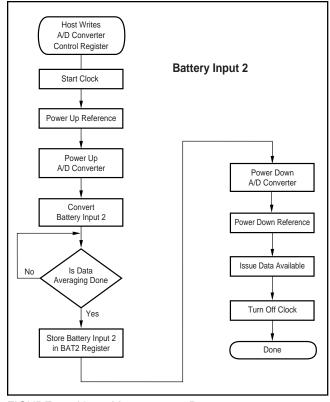

| 0    | 1    | 1    | 0    | Battery Input 1 converted and the results returned to the BAT1 data register.                                                 |

| 0    | 1    | 1    | 1    | Battery Input 2 converted and the results returned to the BAT2 data register.                                                 |

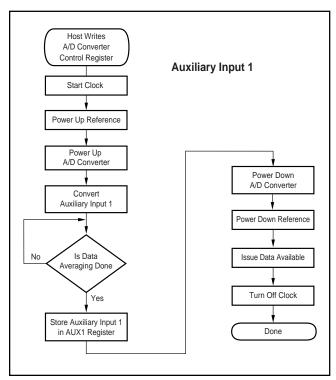

| 1    | 0    | 0    | 0    | Auxiliary Input 1 converted and the results returned to the AUX1 data register.                                               |

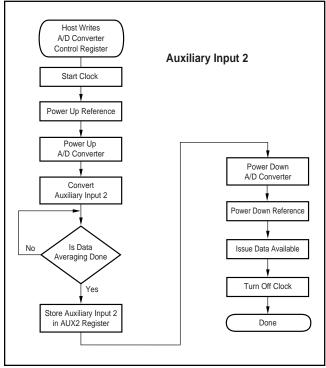

| 1    | 0    | 0    | 1    | Auxiliary Input 2 converted and the results returned to the AUX2 data register.                                               |

| 1    | 0    | 1    | 0    | A temperature measurement is made and the results returned to the temperature measurement 1 data register.                    |

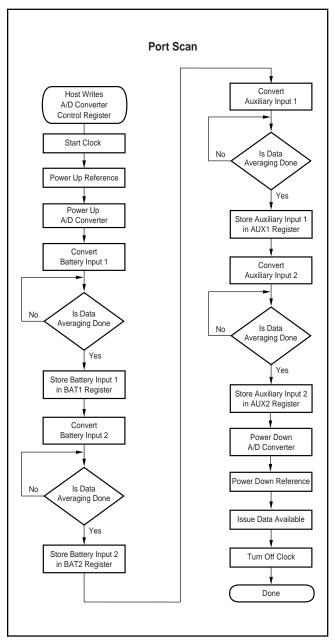

| 1    | 0    | 1    | 1    | Port scan function: Battery Input 1, Battery Input 2, Auxiliary Input 1, and a Auxiliary Input measurements are made          |

|      |      |      |      | and the results returned to the appropriate data registers.                                                                   |

| 1    | 1    | 0    | 0    | A differential temperature measurement is made and the results returned to the temperature measurement 2 data                 |

|      |      |      |      | register.                                                                                                                     |

| 1    | 1    | 0    | 1    | Turn on X+, X- drivers.                                                                                                       |

| 1    | 1    | 1    | 0    | Turn on Y+, Y- drivers.                                                                                                       |

| 1    | 1    | 1    | 1    | Turn on Y+, X- drivers.                                                                                                       |

TABLE VIII. A/D Converter Function Select.

**Bits**[7:6]: AV1, AV0 = Converter Averaging Control. These two bits allow you to specify the number of averages the converter will perform, as shown in Table X. Note that when averaging is used, the STS bit and the  $\overline{DAV}$  output will indicate that the converter is busy until all conversions necessary for the averaging are complete. The default state for these bits is 00, selecting no averaging. These bits are the same whether reading or writing.

| AV1 | AV0 | FUNCTION         |

|-----|-----|------------------|

| 0   | 0   | None             |

| 0   | 1   | 4 Data Averages  |

| 1   | 0   | 8 Data Averages  |

| 1   | 1   | 16 Data Averages |

TABLE X. A/D Conversion Averaging Control.

**Bits**[5:4]: **CL1**, **CL0** = Conversion Clock Control. These two bits specify the internal clock rate which the A/D converter uses when performing a single conversion, as shown in Table XI. These bits are the same whether reading or writing.

| CL1 | CL0 | FUNCTION                                        |

|-----|-----|-------------------------------------------------|

| 0   | 0   | 8MHz Internal Clock Rate—8-Bit Resolution Only  |

| 0   | 1   | 4MHz Internal Clock Rate—10-Bit Resolution Only |

| 1   | 0   | 2MHz Internal Clock Rate.                       |

| 1   | 1   | 1MHz Internal Clock Rate.                       |

TABLE XI. A/D Converter Clock Control.

Bits [3:1]: PV2 – PV0 = Panel Voltage Stabilization Time control. These bits allow you to specify a delay time from the time a pen touch is detected to the time a conversion is started. This allows you to select the appropriate settling time for the touch panel used. Table XII shows the settings of these bits. The default state is 000, indicating a 0ms stabilization time. These bits are the same whether reading or writing.

**Bit 0:** This bit is not used, and is a "don't care" when writing. It will always read as a zero.

| PV2 | PV1 | PV0 | FUNCTION                 |

|-----|-----|-----|--------------------------|

| 0   | 0   | 0   | 0μs Stabilization Time   |

| 0   | 0   | 1   | 100μs Stabilization Time |

| 0   | 1   | 0   | 500μs Stabilization Time |

| 0   | 1   | 1   | 1ms Stabilization Time   |

| 1   | 0   | 0   | 5ms Stabilization Time   |

| 1   | 0   | 1   | 10ms Stabilization Time  |

| 1   | 1   | 0   | 50ms Stabilization Time  |

| 1   | 1   | 1   | 100ms Stabilization Time |

TABLE XII. Panel Voltage Stabilization Time Control.

## D/A CONVERTER CONTROL REGISTER (PAGE 1, ADDRESS 02<sub>H</sub>)

The single bit in this register controls the power down control of the on-board D/A converter. This register is formatted as shown in Table XIII.

**Bit 15: DPD** = D/A Converter Power Down. This bit controls whether the D/A converter is powered up and operational, or powered down. If the D/A converter is powered down, the  $A_{OUT}$  pin will neither sink nor source current.

|   | DPD   |                                          |  |  |  |  |  |  |

|---|-------|------------------------------------------|--|--|--|--|--|--|

|   | VALUE | DESCRIPTION                              |  |  |  |  |  |  |

| ſ | 0     | D/A Converter is Powered and Operational |  |  |  |  |  |  |

| ı | 1     | D/A Converter is Powered Down            |  |  |  |  |  |  |

TABLE XIV. DPD Bit Operation.

## REFERENCE REGISTER (PAGE 1, ADDRESS 03<sub>H</sub>)

The TSC2000 has a register to control the operation of the internal reference. This register is formatted as shown in Table XV.

**Bit 4:** INT = Internal Reference Mode. If this bit is written to a 1, the TSC2000 will use its internal reference; if this bit is a zero, the part will assume an external reference is being supplied. The default state for this bit is to select an external reference (0). This bit is the same whether reading or writing.

|       | ĪNT                         |

|-------|-----------------------------|

| VALUE | DESCRIPTION                 |

| 0     | External Reference Selected |

| 1     | Internal Reference Selected |

TABLE XVI. INT Bit Operation.

Bits [3:2]: DL1, DL0 = Reference Power-Up Delay. When the internal reference is powered up, a finite amount of time is required for the reference to settle. If measurements are made before the reference has settled, these measurements will be in error. These bits allow for a delay time for measurements to be made after the reference powers up, thereby assuring that the reference has settled. Longer delays will be necessary depending upon the capacitance present at the REF pin (see Typical Characteristics).

See Table XVII for the delays. The default state for these bits is 00, selecting a 0ms delay. These bits are the same whether reading or writing.

| MSB<br>BIT 15 | BIT 14 | BIT 13 | BIT 12 | BIT 11 | BIT 10 | BIT 9 | BIT 8 | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | LSB<br>BIT 0 |

|---------------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|--------------|

| DPD           | Х      | Х      | Х      | Х      | Х      | Х     | Х     | Х     | Х     | Х     | Х     | Х     | Х     | Х     | Х            |

TABLE XIII. D/A Converter Control Register.

| MSB<br>BIT 15 | BIT 14 | BIT 13 | BIT 12 | BIT 11 | BIT 10 | BIT 9 | BIT 8 | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | LSB<br>BIT 0 |

|---------------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|--------------|

| Х             | Х      | Х      | X      | Х      | Х      | Х     | Х     | Х     | Х     | Х     | INT   | DL1   | DL0   | PDN   | RFV          |

TABLE XV. Reference Register.

| DL1 | DL0 | DELAY TIME |

|-----|-----|------------|

| 0   | 0   | 0μs        |

| 0   | 1   | 100μs      |

| 1   | 0   | 500μs      |

| 1   | 1   | 1000μs     |

TABLE XVII. Reference Power-Up Delay Settings.

**Bit 1: PDN** = Reference Power Down. If a 1 is written to this bit, the internal reference will be powered down between conversions. If this bit is a zero, the internal reference will be powered at all times. The default state is to power down the internal reference, so this bit will be a 1. This bit is the same whether reading or writing.

|       | PDN                                                    |  |  |  |  |  |  |  |

|-------|--------------------------------------------------------|--|--|--|--|--|--|--|

| VALUE | DESCRIPTION                                            |  |  |  |  |  |  |  |

| 0     | Internal Reference is Powered at All Times             |  |  |  |  |  |  |  |

| 1     | Internal Reference is Powered Down Between Conversions |  |  |  |  |  |  |  |

TABLE XVIII. PDN Bit Operation.

Note that the PDN bit, in concert with the  $\overline{\text{INT}}$  bit, creates a few possibilities for reference behavior. These are detailed in Table XIX.

| INT | PDN | REFERENCE BEHAVIOR                                        |

|-----|-----|-----------------------------------------------------------|

| 0   | 0   | External Reference Used, Internal Reference Powered Down  |

| 0   | 1   | External Reference Used, Interenal Reference Powered Down |

| 1   | 0   | Internal Reference Used, Always Powered Up                |

| 1   | 1   | Internal Reference Used, Will Power Up During Conversions |

|     |     | and Then Power Down                                       |

TABLE XIX. Reference Behavior Possibilities.

**Bit 0:** RFV = Reference Voltage control. This bit selects the internal reference voltage, either 1.25V or 2.5V. The default value is 1.25V. This bit is the same whether reading or writing.

|       | RFV                     |

|-------|-------------------------|

| VALUE | DESCRIPTION             |

| 0     | 1.25V Reference Voltage |

| 1     | 2.5V Reference Voltage  |

TABLE XX. RFV Bit Operation.

## TSC2000 CONFIGURATION CONTROL REGISTER (PAGE 1, ADDRESS $05_{\rm H}$ )

This control register controls the configuration of the precharge and sense times for the touch detect circuit. The register is formatted as shown in Table XXI.

**Bits** [5:3]: PRE[2:0] = Precharge Time Selection Bits. These bits set the amount of time allowed for precharging any pin capacitance on the touch screen prior to sensing if a screen touch is happening.

|      | PRE[2:0] |      |         |  |  |  |  |  |  |  |  |  |  |

|------|----------|------|---------|--|--|--|--|--|--|--|--|--|--|

| PRE2 | PRE1     | PRE0 | TIME    |  |  |  |  |  |  |  |  |  |  |

| 0    | 0        | 0    | 20μs    |  |  |  |  |  |  |  |  |  |  |

| 0    | 0        | 1    | 84μs    |  |  |  |  |  |  |  |  |  |  |

| 0    | 1        | 0    | 276µs   |  |  |  |  |  |  |  |  |  |  |

| 0    | 1        | 1    | 340μs   |  |  |  |  |  |  |  |  |  |  |

| 1    | 0        | 0    | 1.044ms |  |  |  |  |  |  |  |  |  |  |

| 1    | 0        | 1    | 1.108ms |  |  |  |  |  |  |  |  |  |  |

| 1    | 1        | 0    | 1.300ms |  |  |  |  |  |  |  |  |  |  |

| 1    | 1        | 1    | 1.364ms |  |  |  |  |  |  |  |  |  |  |

TABLE XXII. Precharge Times.

Bits [2:0]: SNS[2:0] = Sense Time Selection Bits. These bits set the amount of time the TSC2000 will wait to sense a screen touch between coordinate axis conversions in PENIRQ-controlled mode.

|      |      | SN   | S[2:0]  |

|------|------|------|---------|

| SNS2 | SNS1 | SNS0 | TIME    |

| 0    | 0    | 0    | 32μs    |

| 0    | 0    | 1    | 96μs    |

| 0    | 1    | 0    | 544μs   |

| 0    | 1    | 1    | 608µs   |

| 1    | 0    | 0    | 2.080ms |

| 1    | 0    | 1    | 2.144ms |

| 1    | 1    | 0    | 2.592ms |

| 1    | 1    | 1    | 2.656ms |

TABLE XXIII. Sense Times.

| MSB<br>BIT 15 | BIT 14 | BIT 13 | BIT 12 | BIT 11 | BIT 10 | BIT 9 | BIT 8 | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | LSB<br>BIT 0 |

|---------------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|--------------|

| Х             | Х      | Х      | Х      | Х      | Х      | Х     | Х     | Х     | Х     | PRE2  | PRE1  | PRE0  | SNS2  | SNS1  | SNS0         |

TABLE XXI. Configuration Control Register.

## RESET REGISTER (PAGE 1, ADDRESS 04<sub>H</sub>)

The TSC2000 has a special register, the RESET register, which allows a software reset of the device. Writing the code  $BBXX_H$ , as shown in Table XXIV, to this register will cause the TSC2000 to reset all its registers to their default, power-up values.

Writing any other values to this register will do nothing. Reading this register or any reserved register will result in reading back all 1's, or FFFF<sub>H</sub>.

### **TSC2000 DATA REGISTERS**

The data registers of the TSC2000 hold data results from conversions or keypad scans, or the value of the D/A converter output current. All of these registers default to  $0000_{\rm H}$  upon reset, except the D/A converter register, which is set to  $0080_{\rm H}$ , representing the midscale output of the D/A converter.

## X, Y, $Z_1$ , $Z_2$ , BAT1, BAT2, AUX1, AUX2, TEMP1, AND TEMP2 REGISTERS

The results of all A/D conversions are placed in the appropriate data register, see Tables III and VIII. The data format of the result word, R, of these registers is right-justified, as shown in Table XXV.

## D/A CONVERTER DATA REGISTER (PAGE 0, ADDRESS 0B<sub>H</sub>)

The data to be written to the D/A converter is written into the D/A converter data register, which is formatted as shown in Table XXVI.

## ZERO REGISTER (PAGE 0, ADDRESS 10<sub>H</sub>)

This is a reserved data register, but instead of reading all 1's  $(FFF_H)$ , when read will return all 0's  $(0000_H)$ .

### **OPERATION—TOUCH SCREEN MEASUREMENTS**

As noted previously in the discussion of the A/D converter, several operating modes can be used, which allow great flexibility for the host processor. These different modes will now be examined.

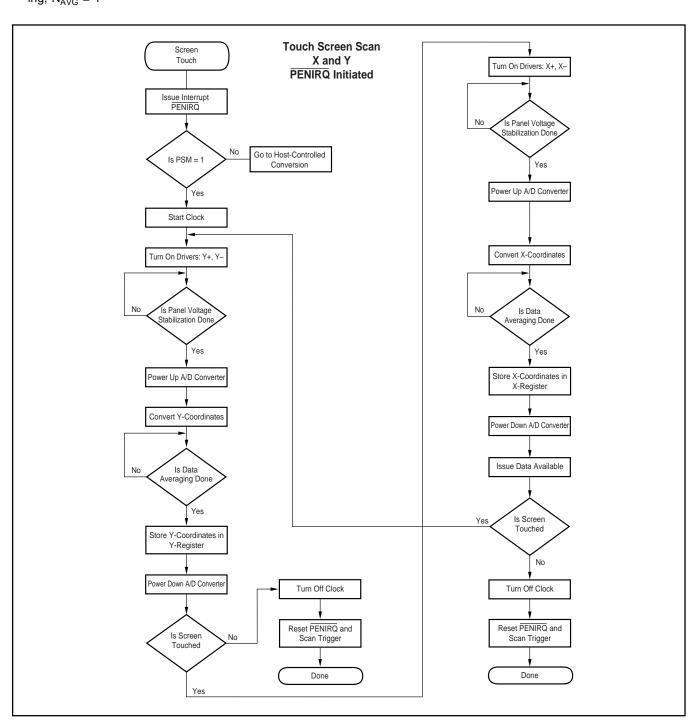

## Conversion Controlled by TSC2000 Initiated at Touch Detect

In this mode, the TSC2000 will detect when the touch panel is touched and cause the PENIRQ line to go LOW. At the same time, the TSC2000 will start up its internal clock. It will then turn on the Y-drivers, and after a programmed Panel Voltage Stabilization time, power up the A/D converter and convert the Y-coordinate. If averaging is selected, several conversions may take place; when data averaging is complete, the Y-coordinate result will be stored in the Y-register.

If the screen is still touched at this time, the X-drivers will be enabled, and the process will repeat, but instead measuring the X-coordinate and storing the result in the X-register.

If only X- and Y-coordinates are to be measured, then the conversion process is complete. See Figure 8 for a flowchart for this process. The time it takes to go through this process depends upon the selected resolution, internal conversion clock rate, averaging selected, panel voltage stabilization time, and precharge and sense times.

| MSB<br>BIT 15 | BIT 14 | BIT 13 | BIT 12 | BIT 11 | BIT 10 | BIT 9 | BIT 8 | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | LSB<br>BIT 0 |

|---------------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|--------------|

| 1             | 0      | 1      | 1      | 1      | 0      | 1     | 1     | X     | Х     | Х     | Х     | Х     | Х     | Х     | Х            |

TABLE XXIV. Reset Register.

| MSB<br>BIT 15 | BIT 14 | BIT 13 | BIT 12 | BIT 11     | BIT 10 | BIT 9 | BIT 8 | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | LSB<br>BIT 0 |

|---------------|--------|--------|--------|------------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|--------------|

| 0             | 0      | 0      | 0      | R11<br>MSB | R10    | R9    | R8    | R7    | R6    | R5    | R4    | R3    | R2    | R1    | R0<br>LSB    |

TABLE XXV. Result Data Format.

| MSB<br>BIT 15 | BIT 14 | BIT 13 | BIT 12 | BIT 11 | BIT 10 | BIT 9 | BIT 8 | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | LSB<br>BIT 0 |

|---------------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|--------------|

| Χ             | Х      | Х      | X      | Х      | Х      | X     | X     | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0           |

TABLE XXVI. D/A Converter Register.

The time needed to get a complete X/Y-coordinate reading can be calculated by:

$t_{\text{COORDINATE}} = 2.5\mu\text{s} + 2(t_{\text{PVS}} + t_{\text{PRE}} + t_{\text{SNS}}) + 2N_{\text{AVG}}\left(N_{\text{BITS}} \bullet \frac{1}{f_{\text{CONV}}} + 4.4\mu\text{s}\right)$  where,

$t_{\text{COORDINATE}}$  = time to complete X/Y-coordinate reading

$t_{PVS}$  = Panel Voltage Stabilization time, see Table XII

$t_{PRE}$  = precharge time, see Table XXII

$t_{SNS}$  = sense time, see Table XXIII

$N_{AVG} = \mbox{number of averages, see Table X; for no averaging, <math display="inline">N_{AVG} = 1$

$N_{BITS}$  = number of bits of resolution, see Table IX

$f_{CONV} = A/D$  converter clock frequency, see Table XI

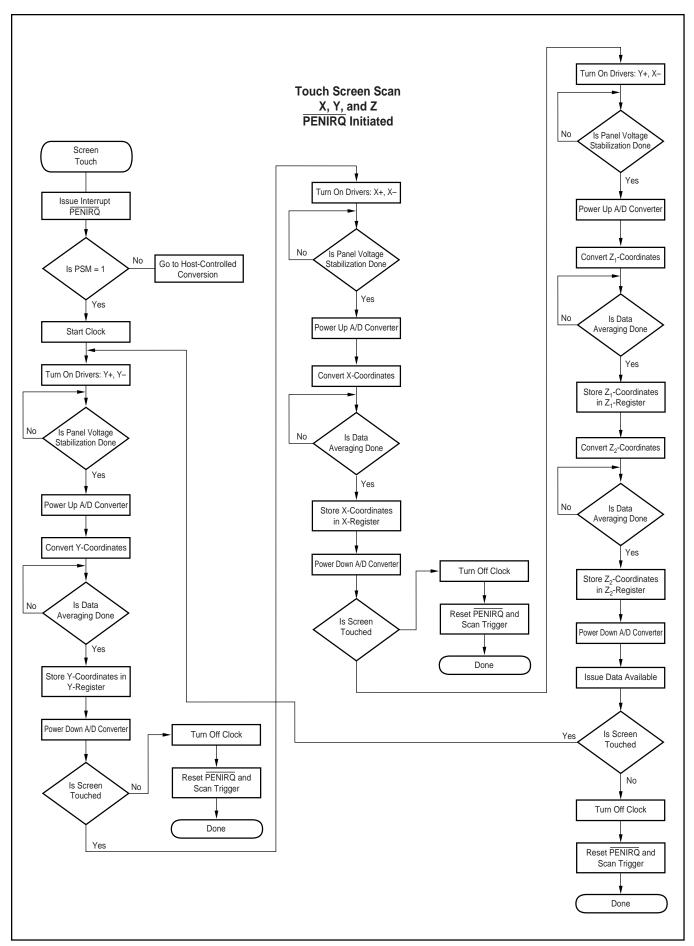

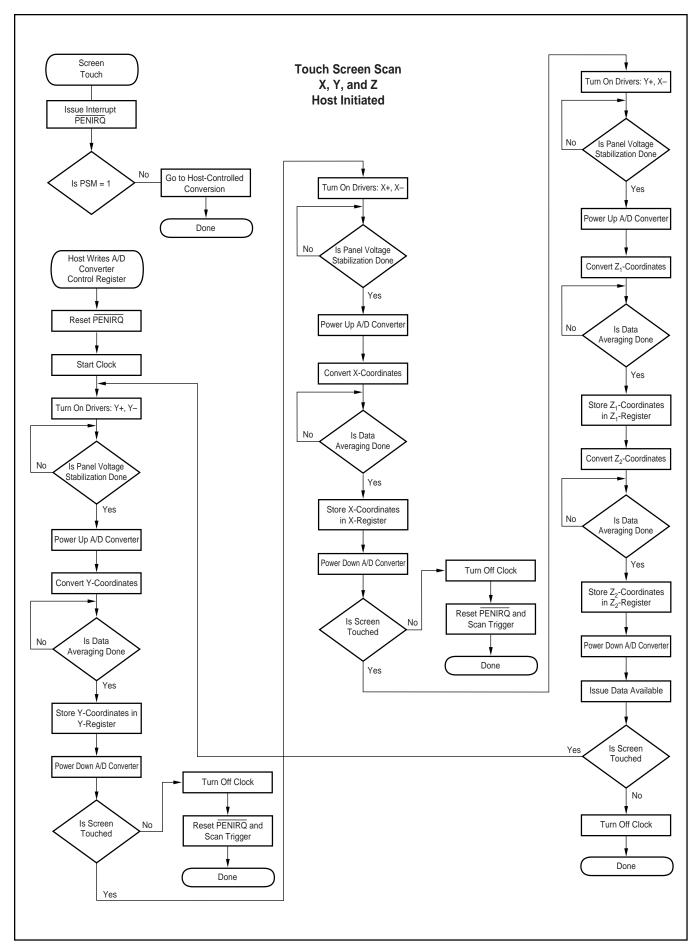

If the pressure of the touch is also to be measured, the process will continue in the same way, but measuring the  $Z_1$  and  $Z_2$  values, and placing them in the  $Z_1$  and  $Z_2$  registers, see Figure 9. As before, this process time depends upon the settings described above. The time for a complete X, Y,  $Z_1$ , and  $Z_2$  coordinate reading is given by:

(4

$$t_{COORDINATE} = 4.75 \mu \text{s} + 3 \left( t_{PVS} + t_{PRE} + t_{SNS} \right) + 4 N_{AVG} \left( N_{BITS} \bullet \frac{1}{f_{CONV}} + 4.4 \mu \text{s} \right)$$

FIGURE 8. X- and Y-Coordinate Touch Screen Scan, Initiated by Touch.

FIGURE 9. X-, Y-, and Z-Coordinate Touch Screen Scan, Initiated by Touch.

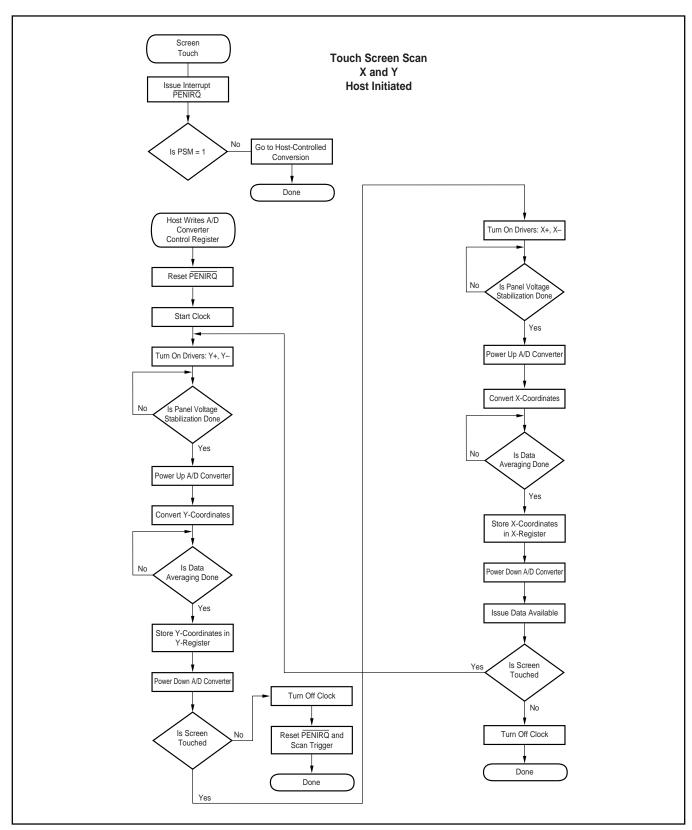

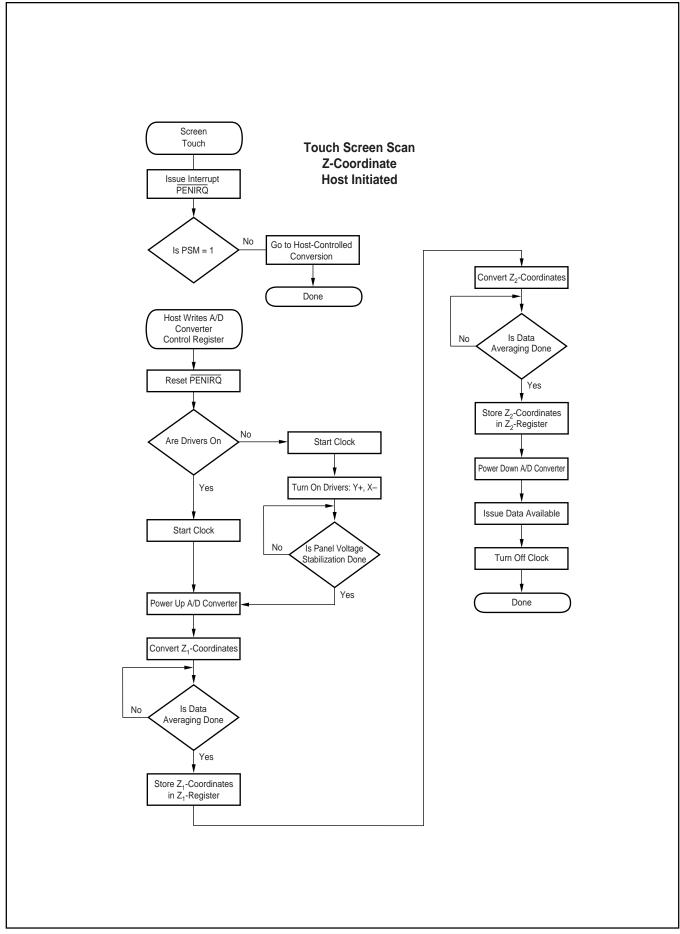

## Conversion Controlled by TSC2000 Initiated By Host Responding to $\overline{\text{PENIRQ}}$

In this mode, the TSC2000 will detect when the touch panel is touched and cause the  $\overline{\text{PENIRQ}}$  line to go LOW. The host will recognize the interrupt request, and then write to the A/D Converter Control register to select one of the touch screen

scan functions. The conversion process then proceeds as described above, and as outlined in Figures 10 through 14.

The main difference between this mode and the previous mode is that the host, not the TSC2000, decides when the touch screen scan begins.

FIGURE 10. X- and Y-Coordinate Touch Screen Scan, Initiated by Host.

FIGURE 11. X-, Y-, and Z-Coordinate Touch Screen Scan, Initiated by Host.

FIGURE 13. Y-Coordinate Reading Initiated by Host.

FIGURE 14. Z-Coordinate Reading Initiated by Host.

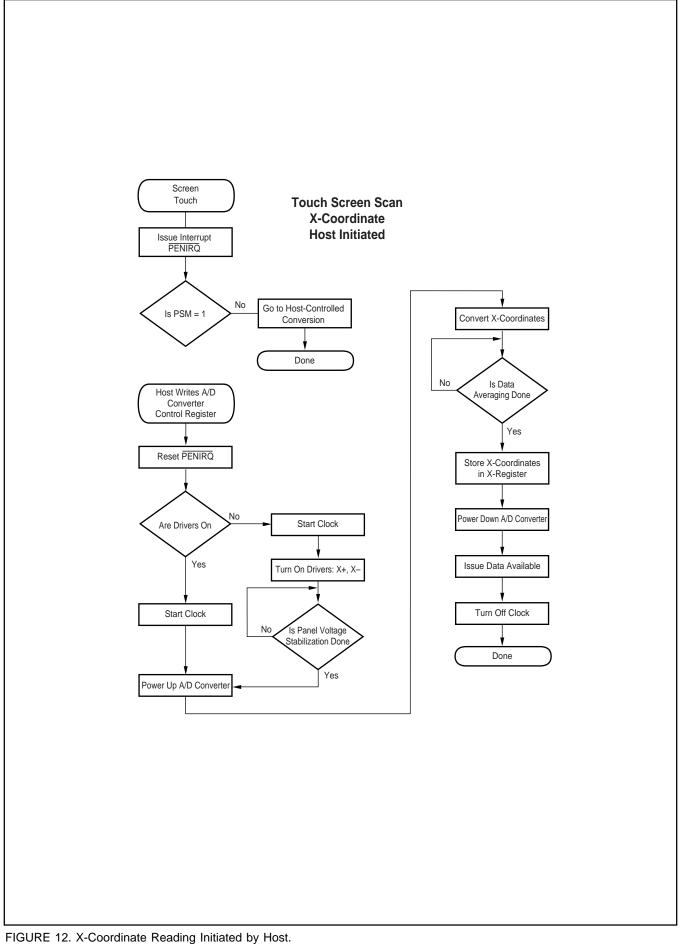

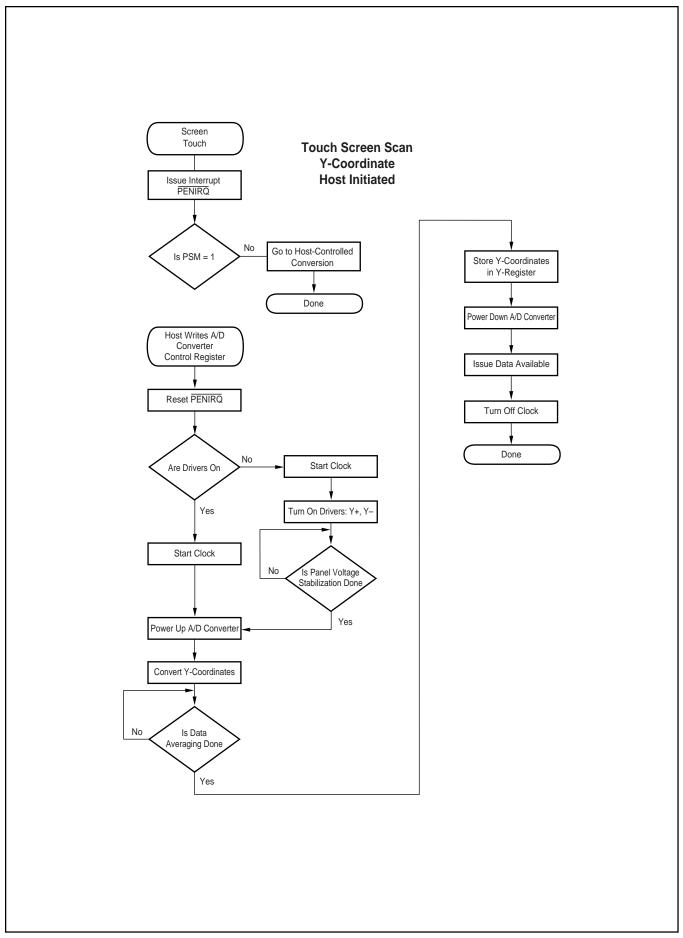

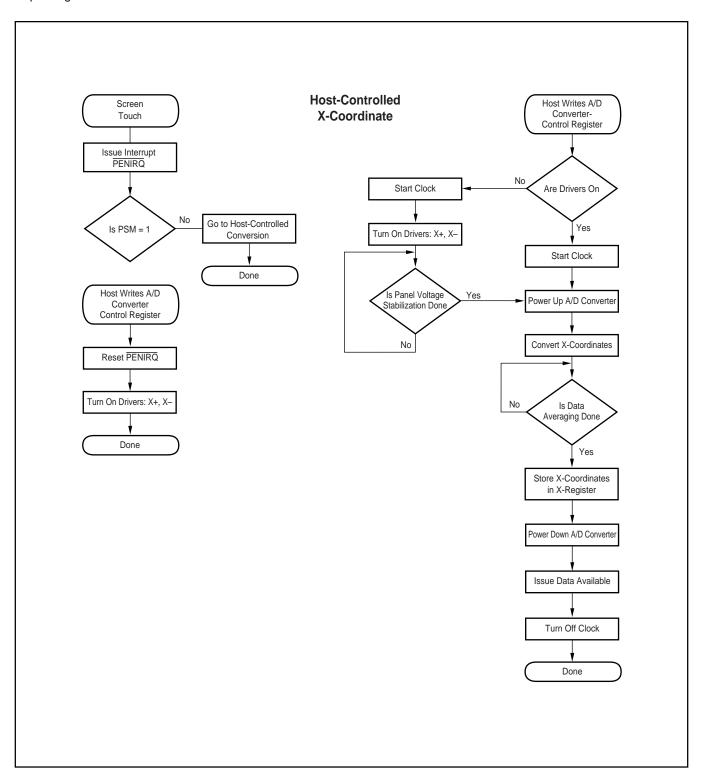

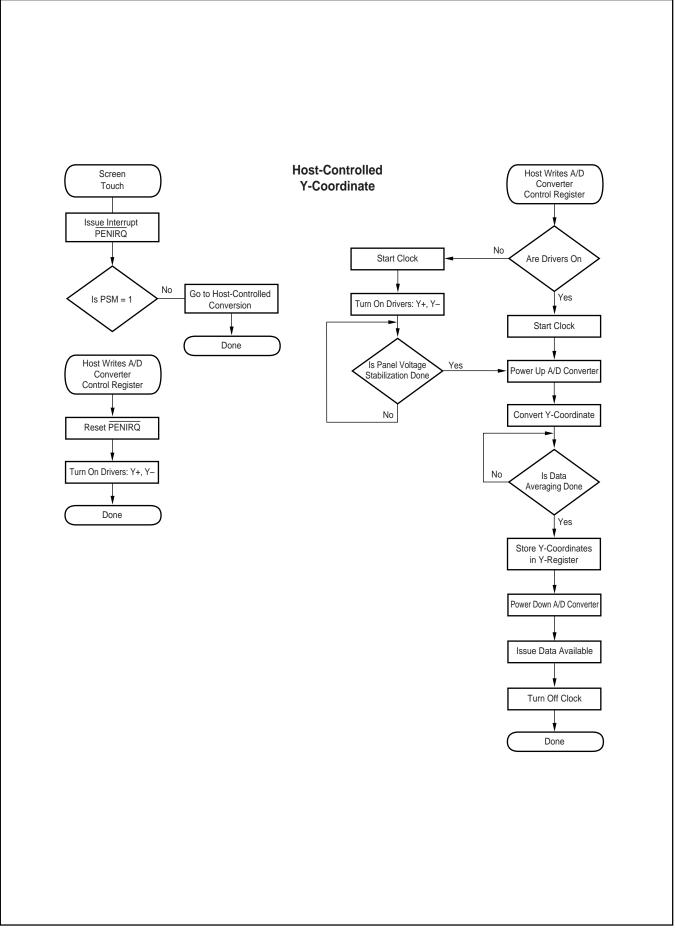

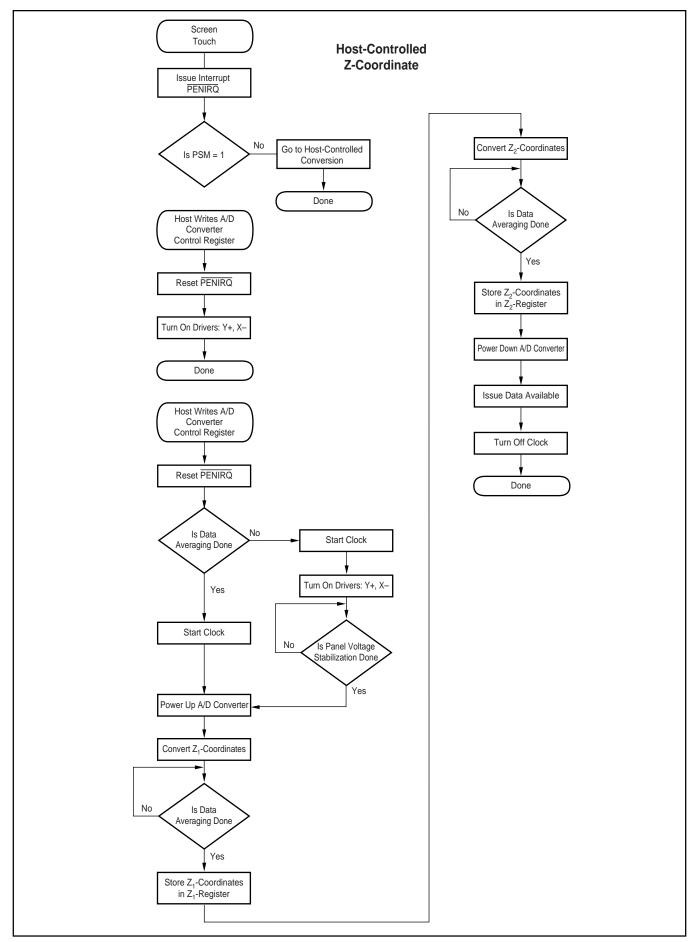

### **Conversion Controlled by the Host**

In this mode, the TSC2000 will detect when the touch panel is touched and cause the PENIRQ line to go LOW. The host will recognize the interrupt request. Instead of starting a sequence in the TSC2000 which then reads each coordinate in turn, the host now must control all aspects of the conversion. Generally, upon receiving the interrupt request, the host will turn on the Y-drivers. After waiting for the settling time, the host will then address the TSC2000 again, this time requesting an X-coordinate conversion.

The process is then repeated for Y- and Z-coordinates. The processes are outlined in Figures 15 through 17.

The time needed to convert any single coordinate under host control (not including the time needed to send the command over the SPI bus) is given by:

$$t_{COORDINATE} = 2.125 \mu s + t_{PVS} + N_{AVG} \left( N_{BITS} \bullet \frac{1}{f_{CONV}} + 4.4 \mu s \right)$$

FIGURE 15. X-Coordinate Reading Controlled by Host.

FIGURE 16. Y-Coordinate Reading Controlled by Host.

FIGURE 17. Z-Coordinate Reading Controlled by Host.

#### **OPERATION—TEMPERATURE MEASUREMENT**

In some applications, such as battery recharging, a measurement of ambient temperature is required. The temperature measurement technique used in the TSC2000 relies on the characteristics of a semiconductor junction operating at a fixed current level. The forward diode voltage ( $V_{BE}$ ) has a well-defined characteristic versus temperature. The ambient temperature can be predicted in applications by knowing the 25°C value of the  $V_{BE}$  voltage and then monitoring the delta of that voltage as the temperature changes.

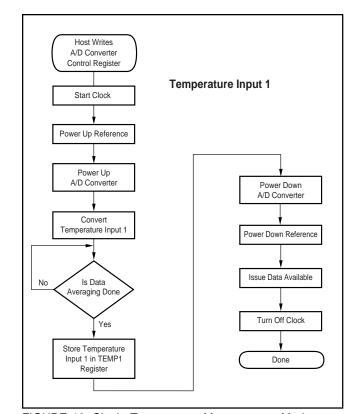

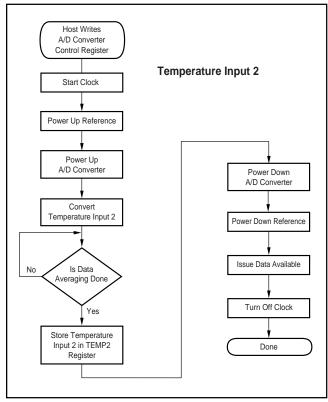

The TSC2000 offers two modes of temperature measurement. The first mode requires calibration at a known temperature, but only requires a single reading to predict the ambient temperature. A diode, as shown in Figure 18, is used during this measurement cycle. This voltage is typically 600mV at +25°C with a 20µA current through it. The absolute value of this diode voltage can vary a few millivolts; the temperature coefficient (TC) of this voltage is very consistent at –2.1mV/°C. During the final test of the end product, the diode voltage would be stored at a known room temperature, in system memory, for calibration purposes by the user. The result is an equivalent temperature measurement resolution of 0.3°C/LSB. This measurement of what is referred to as Temperature 1 is illustrated in Figure 19.

FIGURE 18. Functional Block Diagram of Temperature Measurement Mode.