NOT RECOMMENDED FOR NEW DESIGNS Contact our Technical Support Center at 1-888-INTERSIL or www.intersil.com/tsc

# DATASHEET

Page 1 of 65

**TW2816**

FN7736 Rev. 1.00 May 19, 2017

# 4-Channel Video Decoders for Security Applications

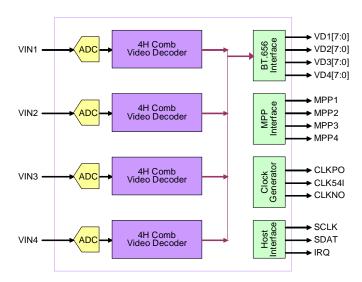

The TW2816 includes four high quality NTSC/ PAL video decoders, which convert analog composite to digital component YCbCr for security application. The TW2816 contains four analog anti-aliasing filters, 10-bit ADCs and proprietary digital gain/clamp controllers and utilizes proprietary techniques for separating luminance & chrominance to reduce both cross-luminance and cross-chrominance artifacts. The TW2816 also adopts the image enhancement techniques such as IF compensation filter, CTI and luminance programmable peaking filter to produce a high quality pictures.

#### **Features**

#### Four Video Decoders

- Accepts all NTSC(M/N/4.43) / PAL(B/D/G/H/I/K/L/M/N/60) standards with auto detection

- Integrated four video analog anti-aliasing filters and 10 bit CMOS ADCs

- High performance adaptive 4H comb filters for all NTSC/PAL standards

- IF compensation filter for improvement of color demodulation

- Color Transient Improvement (CTI)

- Automatic white peak control

- Programmable hue, saturation, contrast, brightness and sharpness

- Proprietary fast video locking system for non-realtime application

- Supports the standard ITU-R BT.656 format or time multiplexed output with 54MHz

- Provides simultaneous four channel Full D1 and CIF time-multiplexed outputs with 54MHz

- Supports a two-wire serial host interface

- Ultra low power consumption (Typical 480mW)

- 100 TQFP package

# **Table of Contents**

| Block Diagram                                               | 4  |

|-------------------------------------------------------------|----|

| Pin Diagram                                                 | 5  |

| Pin Descriptions                                            |    |

| Analog Video Interface Pins                                 |    |

| Digital Video Interface Pins                                | 6  |

| System Control Pins                                         | (  |

| Power and Ground Pins                                       | 7  |

| No Connection                                               | 7  |

| Functional Description                                      | 8  |

| Video Input Formats                                         | 8  |

| Analog-to-Digital Converter                                 | 9  |

| Sync Processing                                             | 1( |

| Automatic Gain Control and Clamping                         | 10 |

| Horizontal Sync Processing                                  | 10 |

| Vertical Sync Processing                                    | 1( |

| Color Decoding                                              | 11 |

| Decimation Filter                                           | 11 |

| Y/C Separation                                              | 12 |

| Luminance Processing                                        | 13 |

| Chrominance Processing                                      | 14 |

| Chrominance Demodulation                                    | 14 |

| ACC (Automatic Color gain control)                          | 15 |

| Chrominance Gain, Offset and Hue Adjustment                 | 15 |

| CTI (Color Transient Improvement)                           | 15 |

| Video Cropping                                              | 16 |

| Output Format                                               | 18 |

| ITU-R BT.656 Format                                         | 18 |

| Two Channel ITU-R BT.656 Time-multiplexed Format with 54MHz | 19 |

| Four Channel CIF Time-multiplexed Format with 54MHz         | 20 |

| Extra Sync Output                                           | 22 |

| Output Enabling Act                                         |    |

| Host Interface                   | 24 |

|----------------------------------|----|

| Serial Interface                 |    |

| Interrupt Interface              | 25 |

| Control Register                 | 26 |

| Register Map                     |    |

| Recommended Value                | 29 |

| Register Description             |    |

| Electrical Information           | 58 |

| Absolute Maximum Ratings         | 58 |

| Recommended Operating Conditions | 58 |

| DC Electrical Parameters         | 59 |

| AC Electrical Parameters         | 60 |

| Decoder Performance Parameter    | 62 |

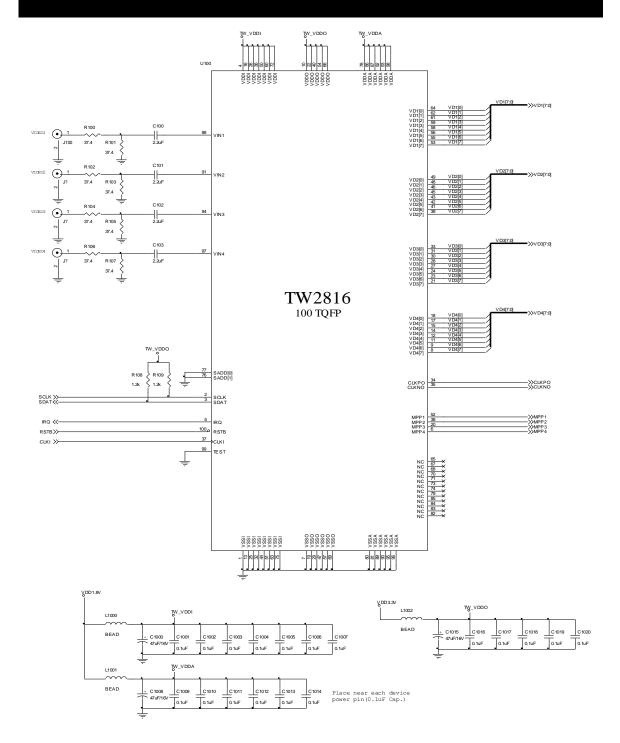

| Recommended Schematic            | 63 |

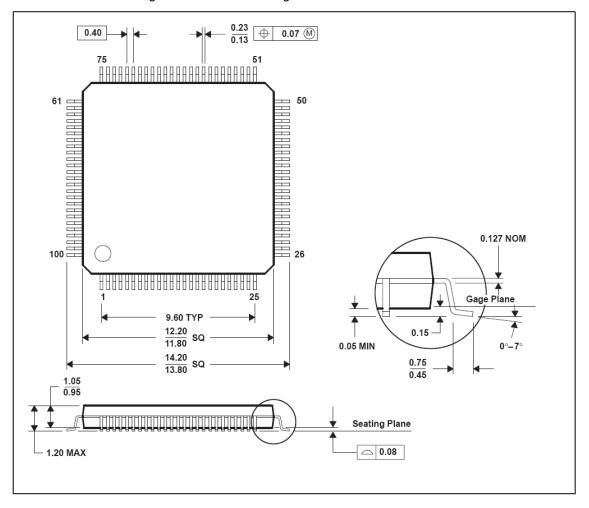

| Package Dimension                | 64 |

| Revision History                 | 65 |

## **Block Diagram**

### **Pin Diagram**

# **Pin Descriptions**

## **Analog Video Interface Pins**

| Name | Number | Type Description |                                     |

|------|--------|------------------|-------------------------------------|

| VIN1 | 88     | Α                | Composite video input of channel 1. |

| VIN2 | 91     | Α                | Composite video input of channel 2. |

| VIN3 | 94     | Α                | Composite video input of channel 3. |

| VIN4 | 97     | Α                | Composite video input of channel 4. |

## **Digital Video Interface Pins**

| Name       | Number                      | Туре | Description                          |

|------------|-----------------------------|------|--------------------------------------|

| VD1[7:0]   | 53,55,56,58,<br>59,61,62,64 | 0    | Video data output of channel 1.      |

| VD2[7:0]   | 39,41,42,43,<br>45,46,48,49 | 0    | Video data output of channel 2.      |

| VD3[7:0] * | 21,23,24,27,<br>28,30,31,33 | 0    | Video data output of channel 3.      |

| VD4[7:0] * | 8,9,11,12,<br>14,15,17,18   | 0    | Video data output of channel 4.      |

| MPP1       | 52                          | 0    | HS/VS/FLD/ACTIVE/NOVID of channel 1. |

| MPP2       | 38                          | 0    | HS/VS/FLD/ACTIVE/NOVID of channel 2. |

| MPP3*      | 20                          | 0    | HS/VS/FLD/ACTIVE/NOVID of channel 3. |

| MPP4*      | 6                           | 0    | HS/VS/FLD/ACTIVE/NOVID of channel 4. |

Note: \* Not supported for TW2816H

## **System Control Pins**

| Name      | Number | Туре | Description                  |

|-----------|--------|------|------------------------------|

| RSTB      | 100    | I    | System reset.                |

| CLK54I    | 37     | I    | 54MHz system clock input.    |

| CLKPO     | 34     | 0    | 27/54MHz clock output.       |

| CLKNO     | 35     | 0    | 27/54MHZ clock output.       |

| TEST      | 99     | I    | Test pin. Connect to ground. |

| SCLK      | 2      | I    | Serial control clock line.   |

| SDAT      | 3      | Ю    | Serial control data line.    |

| SADD[1:0] | 76,77  | I    | Serial control address.      |

| IRQ       | 5      | 0    | Interrupt request output.    |

### **Power and Ground Pins**

| Name | Number                                              | Туре | Description                                  |

|------|-----------------------------------------------------|------|----------------------------------------------|

| VDDI | 4,16,26,<br>36,50,60,72                             | Р    | 1.8V Power for internal logic.               |

| VDDO | 10,22,40,<br>54,66                                  | Р    | 3.3V Power for output driver.                |

| VSS  | 1,7,13,19,<br>25,29,32,44,<br>47,51,57,63,<br>69,75 | G    | Ground for internal logic and output driver. |

| VDDA | 87,92,93,98,<br>78,86                               | Р    | 1.8V Power for analog video.                 |

| VSSA | 89,90,95,96,<br>80,81                               | G    | Ground for analog video.                     |

## **No Connection**

| Name | Number                                      | Туре | Description   |

|------|---------------------------------------------|------|---------------|

| NC   | 65,67,68,70,<br>71,73,74,79,<br>82,83,84,85 | NC   | No Connection |

# **Functional Description**

### **Video Input Formats**

The TW2816 supports all NTSC/PAL standard formats and has built-in automatic standard detection circuit. The following Table1 shows the identified standards. Automatic standard detection can be overridden by writing the value into the IFMTMAN and IFORMAT register (0x01, 0x11, 0x21, 0x31). Even in no-video status, the device can be forced to free-run in a particular video standard mode for fast locking by programming IFORMAT register.

Table1 Input Video Format Supported

| Format              | Line/Fv (Hz) | Fh (KHz) | Fsc (MHz)  |  |  |

|---------------------|--------------|----------|------------|--|--|

| NTSC-M*<br>NTSC-J   | 525/59.94    | 15.734   | 3.579545   |  |  |

| NTSC-4.43*          | 525/59.94    | 15.734   | 4.43361875 |  |  |

| NTSC-N              | 625/50       | 15.625   | 3.579545   |  |  |

| PAL-BDGHI<br>PAL-N* | 625/50       | 15.625   | 4.43361875 |  |  |

| PAL-M*              | 525/59.94    | 15.734   | 3.57561149 |  |  |

| PAL-NC              | 625/50       | 15.625   | 3.58205625 |  |  |

| PAL-60              | 525/59.94    | 15.734   | 4.43361875 |  |  |

Note: \* 7.5 IRE Setup

### **Analog-to-Digital Converter**

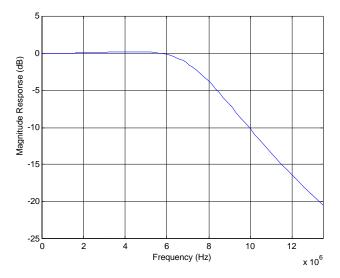

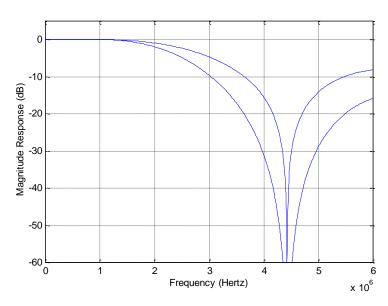

The TW2816 contains four 10-bit ADC (Analog to Digital Converters) to digitize the analog video inputs. The ADC can be put into power-down mode by the ADC\_PWDN (0x50) register. The TW2816 also contains an anti-aliasing filter to prevent out-of-band frequency in analog video input signal. So there is no need of external components in analog input pin except ac coupling capacitor and termination resistor. The following Fig1 shows the frequency response of the anti-aliasing filter.

Fig1 The frequency response of anti-aliasing filter

### **Sync Processing**

The sync processor of TW2816 detects horizontal and vertical synchronization signals in the composite. The TW2816 utilizes proprietary technology for locking to weak, noisy, or unstable signals such as those from on-air signal and fast forward or backward of VCR system.

#### **Automatic Gain Control and Clamping**

A patented digital gain and clamp control circuit restores the ac coupled video signal to a fixed do level. The clamping circuit provides line-by-line restoration of the video pedestal level to a fixed do reference voltage. In no AGC mode, the gain control circuit adjusts only the video sync gain to achieve desired sync amplitude so that the active video is bypassed regardless of the gain control. But when AGC mode is enabled, both active video and sync are adjusted by the gain control. The range of AGC is from –6dB to 18dB approximately. Additionally, an automatic white peak control circuit is included to prevent saturation in the case of abnormal proportion between sync and white peak level.

#### **Horizontal Sync Processing**

The horizontal synchronization processing contains a sync separator, a PLL and the related decision logic. The horizontal sync separator detects the horizontal sync by examining low-pass filtered video input whose level is lower than a threshold. Additional logic is also used to avoid false detection on glitches. The horizontal PLL locks onto the extracted horizontal sync in all conditions to provide jitter free image output. In case the horizontal sync is missing, the PLL is on free running status that matches the standard raster frequency.

#### **Vertical Sync Processing**

The vertical sync separator detects the vertical synchronization pattern in the input video signals. The field status is determined at vertical synchronization time. When the location of the detected vertical sync is inline with a horizontal sync, it indicates a frame start or the odd field start. Otherwise, it indicates an even field.

### **Color Decoding**

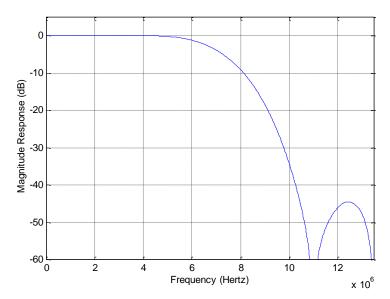

#### **Decimation Filter**

The digitized composite video data at 2X pixel clock rate first passes through decimation filter. The decimation filter is required to achieve optimum performance and prevent high frequency components from being aliased back into the video image. Fig2 shows the characteristic of the decimation filter.

Fig2 The Characteristic of the Decimation Filter

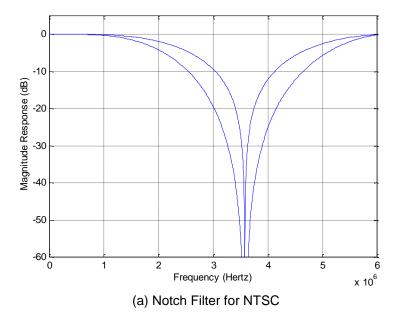

#### Y/C Separation

A proprietary 4H adaptive comb filter is used for high quality luminance/chrominance separation from NTSC/PAL composite video signals. The 4H adaptive comb filter improves the luminance resolution and reduces noise such as cross-luminance and cross-color. The adaptive algorithm eliminates most of errors without introducing new artifacts or noise. To accommodate some viewing preferences, additional chrominance trap filters are also available in the luminance path. The Fig3 show the frequency response of notch filter for each system NTSC and PAL.

#### (b) Notch Filter for PAL

Fig3 The Characteristics of Luminance Notch Filter for PAL

### **Luminance Processing**

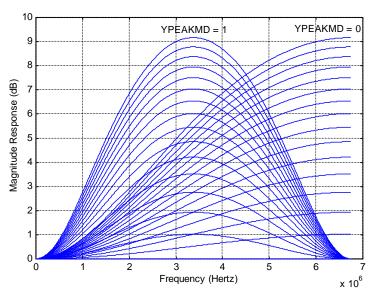

The luminance signal is separated by adaptive comb or trap filter is then fed to a peaking circuit. The peaking filter enhances the high frequency components of the luminance signal via the YPEAK\_GN (0x0B, 0x1B, 0x2B, 0x3B) register. The Fig4 shows the characteristics of the peaking filter for four different gain modes.

Fig4 The Characteristic of Luminance Peaking filter

The picture contrast and brightness adjustment is provided through CONT (0x09, 0x19, 0x29, 0x39) and BRT (0x0A, 0x1A, 0x2A, 0x3A) registers. The contrast adjustment range is from approximately 0 to 200 percent, and the brightness adjustment is in the range of  $\pm 25$  IRE.

### **Chrominance Processing**

#### **Chrominance Demodulation**

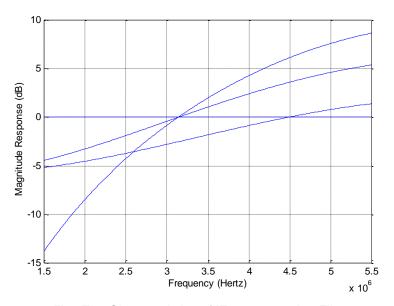

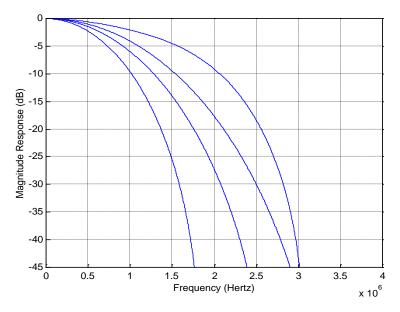

The chrominance demodulation is done by first quadrature mixing for NTSC and PAL. The mixing frequency is equal to the sub-carrier frequency of NTSC and PAL. After the mixing, a LPF is used to remove 2X carrier signal and yield chrominance components. The LPF characteristic can be selected for optimized transient color performance. In case of a mistuned IF source, IF compensation filter makes up for any attenuation at higher frequencies or asymmetry around the color sub-carrier. The gain for the upper chrominance side band is controlled by IFCOMP (0x47) register. The Fig5 and Fig6 show the frequency response of IF-compensation filter and chrominance LPF.

Fig5 The Characteristics of IF-compensation Filter

Fig6 The Characteristics of Chrominance Low Pass Filter

#### **ACC (Automatic Color gain control)**

The ACC (Automatic Color gain Control) compensates for reduced amplitudes caused by high frequency suppression in video signal. The range of ACC is from -6dB to 30dB approximately. For black & white video or very weak & noisy signals, the color will be off by the internal color killing circuit. The color killer function can also be always enabled or disabled by programming CKIL (0x0C, 0x1C, 0x2C, 0x3C) register.

#### **Chrominance Gain, Offset and Hue Adjustment**

The color saturation can be adjusted by changing the register SAT (0x08, 0x18, 0x28, 0x38). The Cb and Cr gain can be also adjusted independently by programming UGAIN (0x49) and VGAIN (0x4A) register. Likewise, the Cb and Cr offset can be programmed through U\_OFF (0x4B) and V\_OFF (0x4C) registers. Hue control is achieved with phase shift of the digitally controlled oscillator. The phase shift can be programmed through HUE (0x07, 0x17, 0x27, 0x37) register.

#### **CTI (Color Transient Improvement)**

A programmable Color Transient Improvement (CTI) is provided to enhance the color bandwidth. Low level noise enhancement can be suppressed by a programmable coring logic. Overshoot and undershoot are also removed by special circuit to prevent false color generation at the color edge.

### **Video Cropping**

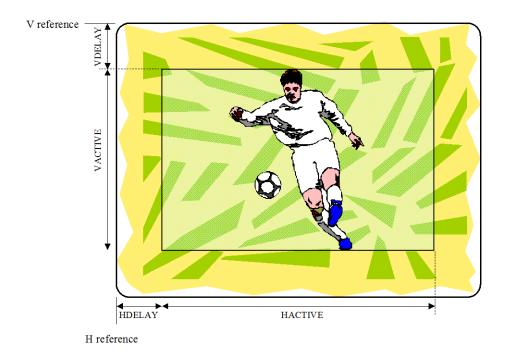

The cropping function allows only subsection of a video image to be output. The active video region is determined by HDELAY, HACTIVE, VDELAY and VACTIVE register as illustrated in Fig7. The first active line is defined by the VDELAY register and the first active pixel is defined by the HDELAY register. The VACTIVE register can be programmed to define the number of active lines in a video field, and the HACTIVE register can be programmed to define the number of active pixels in a video line.

The horizontal delay register HDELAY determines the number of pixel delays between the horizontal reference and the leading edge of the active region. The horizontal active register HACTIVE determines the number of active pixels to be processed. Note that these values are referenced to the pixel number before scaling. Therefore, even if the scaling ratio is changed, the active video region used for scaling remains unchanged as set by the HDEALY and HACTIVE register. In order for the cropping to work properly, the following equation should be satisfied.

HDELAY + HACTIVE < Total number of pixels per line

Where the total number of pixels per line is 858 for 60Hz and 864 for 50Hz

To process full size region, the HDELAY should be set to 32 and HACTIVE set to 720 for both 60Hz and 50Hz system.

The vertical delay register VDELAY determines the number of line delays from the vertical reference to the start of the active video lines. The vertical active register (VACTIVE) determines the number of lines to be processed. These values are referenced to the incoming scan lines before the vertical scaling. In order for the vertical cropping to work properly, the following equation should be satisfied.

VDELAY + VACTIVE < Total number of lines per field

Where the total number of lines per field is 262 for 60Hz and 312 for 50Hz

To process full size region, the VDELAY should be set to 7 and VACTIVE set to 240 for 60Hz and the VDELAY should be also set to 4 and VACTIVE set to 288 for 50Hz.

Fig7 The Effect of Cropping Registers

### **Output Format**

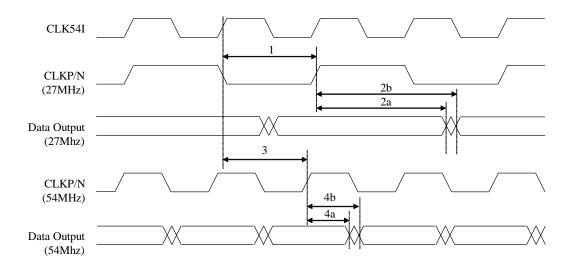

The TW2816 supports a standard ITU-R BT.656 format. All video data and timing signal of four channels are synchronous with the pins CLKPO or CLKNO output. Therefore, CLKPO or CLKNO can be connected to four channel interfaces for synchronizing data. And, the phase of CLKPO or CLKNO can be controlled by 2ns unit via the CLKP\_DEL or CLKN\_DEL (0x4D) registers independently.

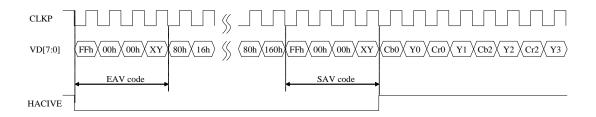

#### **ITU-R BT.656 Format**

In ITU-R BT.656 format, SAV and EAV sequences are inserted into the data stream to indicate the active video time. It is noted that the number of active pixels per line is constant in this mode regardless of the actual incoming line length. The output timing is illustrated in Fig8. The SAV and EAV sequences are shown in Table2. An optional set of 656 SAV/EAV code sequence can be enabled to identify no-video status using the NOVID\_656 bit (0x43).

Fig8 Timing Diagram of ITU-R BT.656 format

|        | Condition     | on         | <b>656</b> l | FVH V    | /alue | SAV/EAV Code Sequence |        |        |        |         |

|--------|---------------|------------|--------------|----------|-------|-----------------------|--------|--------|--------|---------|

| Field  | V time H time |            | F            | V        | Н     | First                 | Second | Third  | For    | urth    |

| i ieiu | v tillie      | i i tiiiie | •            | <b>V</b> | - 1 1 | 1 1131                | Second | Tilliu | Normal | Option* |

| EVEN   | Blank         | EAV        | 1            | 1        | 1     | 0xFF                  | 0x00   | 0x00   | 0xF1   | 0x71    |

| EVEN   | Blank         | SAV        | 1            | 1        | 0     | 0xFF                  | 0x00   | 0x00   | 0xEC   | 0x6C    |

| EVEN   | Active        | EAV        | 1            | 0        | 1     | 0xFF                  | 0x00   | 0x00   | 0xDA   | 0x5A    |

| EVEN   | Active        | SAV        | 1            | 0        | 0     | 0xFF                  | 0x00   | 0x00   | 0xC7   | 0x47    |

| ODD    | Blank         | EAV        | 0            | 1        | 1     | 0xFF                  | 0x00   | 0x00   | 0xB6   | 0x36    |

| ODD    | Blank         | SAV        | 0            | 1        | 0     | 0xFF                  | 0x00   | 0x00   | 0xAB   | 0x2B    |

| ODD    | Active        | EAV        | 0            | 0        | 1     | 0xFF                  | 0x00   | 0x00   | 0x9D   | 0x1D    |

| ODD    | Active        | SAV        | 0            | 0        | 0     | 0xFF                  | 0x00   | 0x00   | 0x80   | 0x00    |

Note: \* Option includes video loss information in ITU-R BT.656

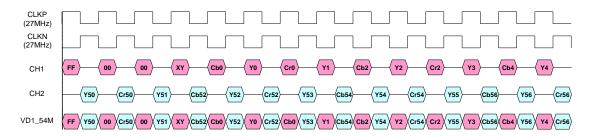

#### Two Channel ITU-R BT.656 Time-multiplexed Format with 54MHz

The TW2816 supports two channel ITU-R BT.656 time-multiplexed format with 54MHz that is useful to security application requiring two channel outputs through one channel video port. The DUAL\_CH (0x0D/0x1E/0x2E/0x3E) register enables the dual ITU-R BT.656 time-multiplexed format and the SEL\_CH (0x0D/0x1E/0x2E/0x3E) register selects another channel output to be multiplexed with its own channel on each VD pins. To de-multiplex the time-multiplexed data in the back end chip, the channel ID can be inserted in the data stream using the CHID (0x42) register. Two kinds of channel ID format can be supported. One is horizontal blanking code with channel ID and the other is ITU-R BT.656 sync code with channel ID. The following Fig9 illustrates the timing diagram in the case of CH1 and CH2 time-multiplexed output through CH1 video output port.

g9 Timing Diagram of Two Channel Time-multiplexed Format with 54MHz

FN7736 Rev. 1.00 Page 19 of 65

May 19, 2017

Fi

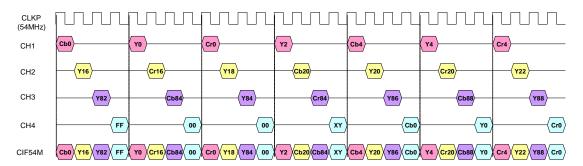

#### Four Channel CIF Time-multiplexed Format with 54MHz

Four channel CIF (360x480) time-multiplexed format is also provided for specific security application using the CIF\_54M (0x75) register. For this format, each channel ITU-R BT.656 data stream is down-sampled into 13.5MHz ITU-R BT.656 data stream except the sync code. To reject an aliasing noise in this format, the HSCL LPF (0x71) register should be set to high. Optionally, the vertical scaling can also be enabled to support Quad (360x240) format using the VSCL\_ENA (0x71) register. Then, these four 13.5MHz ITU-R BT.656 data stream are time-multiplexed into 54MHz data stream. This format requires only one channel video port to transfer whole four channel CIF data independently so that it can be supported simultaneously with two channel Full D1 ITU-R BT.656 time-multiplexed format through the other video ports. To de-multiplex the time-multiplexed data in the back end chip, the channel ID can be inserted in the data stream using the CHID (0x42) register. Two kinds of channel ID format can be supported. One is horizontal blanking code with channel ID and the other is ITU-R BT.656 sync code with channel ID. Optionally, when the vertical scaling is enabled, the ITU-R BT.656 sync code will be skipped in the invalid line through the VSCL SYNC (0x71) register. The following Fig10 and Table3 illustrate the timing diagram and detailed channel ID format for four channel CIF time-multiplexed format with 54MHz.

g10 Timing Diagram of 4 Ch CIF Time-multiplexed Format with 54MHz

Fi

Table3 The Channel ID Format for 4 Ch CIF Time-multiplexed Format with 54MHz

| Condition |        |        | 656 | FVH V | alue | SAV/EAV Code Sequence |        |       |                    |      |                    |                    |

|-----------|--------|--------|-----|-------|------|-----------------------|--------|-------|--------------------|------|--------------------|--------------------|

| Field     | Vtime  | Htime  | F   | V     | Н    | First Second          |        | Third |                    | Fo   | urth               |                    |

| Field     | vuille | Tiulle |     | V     | ''   | FIISt                 | Second | miu   | Ch1                | Ch2  | Ch3                | Ch4                |

| EVEN      | Blank  | EAV    | 1   | 1     | 1    | 0xFF                  | 0x00   | 0x00  | 0xF0               | 0xF1 | 0xF2               | 0xF3               |

| EVEN      | Blank  | SAV    | 1   | 1     | 0    | 0xFF                  | 0x00   | 0x00  | 0xE0               | 0xE1 | 0xE2               | 0xE3               |

| EVEN      | Active | EAV    | 1   | 0     | 1    | 0xFF                  | 0x00   | 0x00  | 0xD0               | 0xD1 | 0xD2               | 0xD3               |

| EVEN      | Active | SAV    | 1   | 0     | 0    | 0xFF                  | 0x00   | 0x00  | 0xC0               | 0xC1 | 0xC2               | 0xC3               |

| ODD       | Blank  | EAV    | 0   | 1     | 1    | 0xFF                  | 0x00   | 0x00  | 0xB0               | 0xB1 | 0xB2               | 0xB3               |

| ODD       | Blank  | SAV    | 0   | 1     | 0    | 0xFF                  | 0x00   | 0x00  | 0xA0               | 0xA1 | 0xA2               | 0xA3               |

| ODD       | Active | EAV    | 0   | 0     | 1    | 0xFF                  | 0x00   | 0x00  | 0x9 <mark>0</mark> | 0x91 | 0x9 <mark>2</mark> | 0x9 <mark>3</mark> |

| ODD       | Active | SAV    | 0   | 0     | 0    | 0xFF                  | 0x00   | 0x00  | 0x8 <mark>0</mark> | 0x81 | 0x8 <mark>2</mark> | 0x8 <mark>3</mark> |

(a) ITU-R BT.656 Sync Code with Channel ID

| Channel | Н     | Blanking Code with Channe | ID                  |

|---------|-------|---------------------------|---------------------|

| Onamici | Y     | Cr                        |                     |

| Ch1     | 8'h10 | 8'h80                     | 8'h80               |

| Ch2     | 8'h11 | 8'h81                     | 8'h81               |

| Ch3     | 8'h12 | 8'h82                     | 8'h82               |

| Ch4     | 8'h13 | 8'h83                     | 8'h8 <mark>3</mark> |

(b) Horizontal Blanking Code with Channel ID

#### **Extra Sync Output**

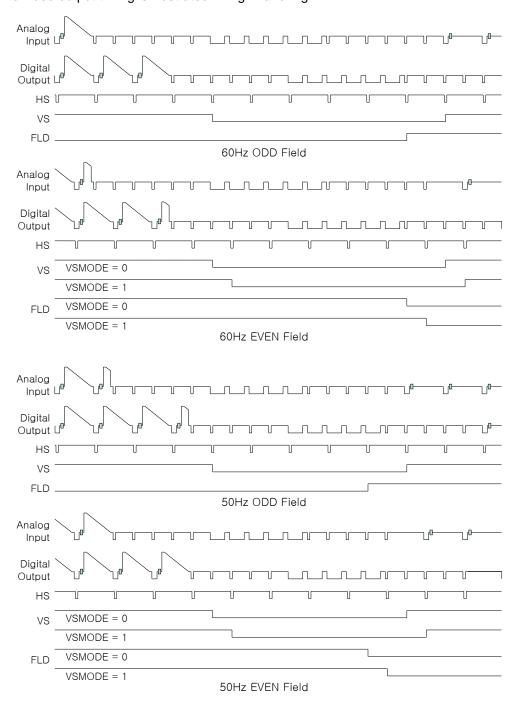

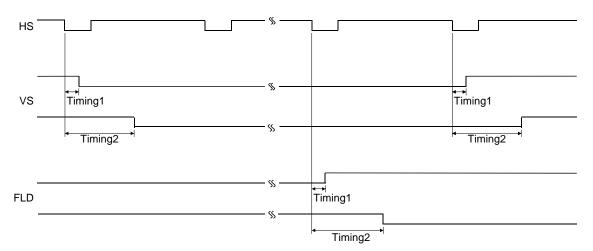

The additional timing information such as syncs and field flag are also supported through the MPP pins. The video output timing is illustrated in Fig11 and Fig12.

Fig11 Vertical Timing for 60Hz / 50Hz Video

$\label{thm:condition} Timing1: 40 \ system \ clock(54MHz) \ for \ the \ Even \ field \ with \ VSMODE=1 \ or \ Odd \ field \ Timing2: 1760 \ system \ clock(54MHz) \ for \ the \ Even \ field \ with \ VSMODE=0$

Fig12 Horizontal and Vertical Timing in Video Output

#### **Output Enabling Act**

After power-up, the TW2816 registers have unknown values. The RSTB pin must be asserted and released to bring all registers to its default values. After reset, the TW2816 data outputs are tristated. The OE (0x43) register should be written after reset to enable outputs desired.

### **Host Interface**

#### **Serial Interface**

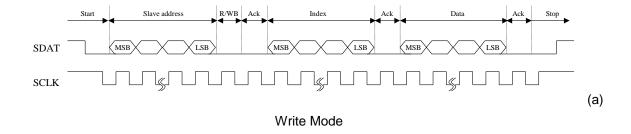

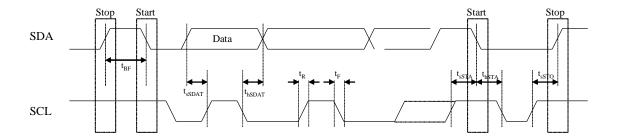

The two wire serial bus interface is used to allow an external micro-controller to write to or read from the data through the TW2816 register. The SCLK is the serial clock and SDAT is the data line. Both lines are pulled high by the resistors connected to VDD. The SADD[1:0] defines two LSB of the slave device address by tying the SADD pins either to VDD or GND.

| Ī |   |   | S | lave Addres | ss |         |         | R/W                   |

|---|---|---|---|-------------|----|---------|---------|-----------------------|

|   | 0 | 1 | 0 | 1           | 0  | SADD[1] | SADD[0] | 1 = Read<br>0 = Write |

The TW2816 supports auto index increments in write/read mode if the data are in sequential order. Data transfer rate on the bus is up to 400 Kbits/s.

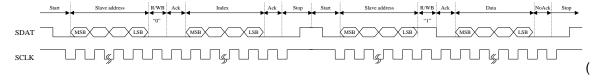

b) Read Mode Fig13 Timing Chart of Serial Interface

#### **Interrupt Interface**

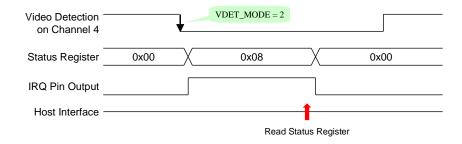

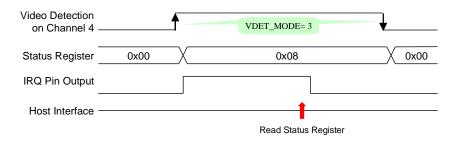

The TW2816 provides the interrupt request function using an IRQ pin so that the host does not need to waste much resource to detect video from TW2816. To use interrupt request function, the interrupt request should be enabled by the IRQENA (0x5C) and polarity of the IRQ pin should be selected by the IRQPOL (0x5C). Also, each channel of video detection should be enabled by the VDET\_ENA (0x5B). Then, the interrupt mode should be defined by the VDET\_MODE (0x5C) that control the time to request interrupt and set the status register VDET\_STATE (0x5A). The Fig14 shows operation of interrupt when the VDET\_MODE are 2 and 3. The IRQ pin is cleared automatically by reading the VDET\_STATE. When the VDET\_MODE is 1 or 2, the status register VDET\_STATE will also be cleared automatically by reading VDET\_STATE. However, when the VDET\_MODE are 3, the status register VDET\_STATE will not be cleared automatically, but has the same value as actual status of video detection flag.

(a) Status Register of Automatic Cleared Mode

(b) Status Register same as Video Detection Flag Mode Fig14 Timing Diagram of Interrupt Interface

## **Control Register**

### Register Map

|      | Add  | Iress |      | Mnemonic  | BIT7         | BIT6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | BIT5        | BIT4                                 | BIT3          | BIT2       | BIT1         | BIT0        |  |

|------|------|-------|------|-----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------------------------------|---------------|------------|--------------|-------------|--|

| CH1  | CH2  | СНЗ   | CH4  | Milemonic | БП7          | ыю                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ыгэ         | DI14                                 | ыз            | DIIZ       | DITT         | БПО         |  |

| 0x00 | 0x10 | 0x20  | 0x30 | VIDSTAT * |              | DET_FORMAT* DET_COLOR* LOCK_COLOR* LOCK_GAIN* LOCK_GAIN |             |                                      |               | LOCK_OFST* | LOCK_HPLL*   |             |  |

| 0x01 | 0x11 | 0x21  | 0x31 | FORMAT    | IFMTMAN      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IFORMAT     |                                      | AGC           | PEDEST     | DET_NONSTD * | DET_FLD60 * |  |

| 0x02 | 0x12 | 0x22  | 0x32 | HDELAY    |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             | HDEL                                 | AY [7:0]      |            |              |             |  |

| 0x03 | 0x13 | 0x23  | 0x33 | HACTIVE   |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             | HACT                                 | IVE [7:0]     |            |              |             |  |

| 0x04 | 0x14 | 0x24  | 0x34 | VDELAY    | HDELAY [7:0] |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |                                      |               |            |              |             |  |

| 0x05 | 0x15 | 0x25  | 0x35 | VACTIVE   |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             | HACT                                 | HACTIVE [7:0] |            |              |             |  |

| 0x06 | 0x16 | 0x26  | 0x36 | MSB_ACTV  | 0            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | VACTIVE [8] | VDELAY [8]                           | HACTI         | /E [9:8]   | HDELA        | Y [9:8]     |  |

| 0x07 | 0x17 | 0x27  | 0x37 | HUE       |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             | Н                                    | IUE           |            |              |             |  |

| 0x08 | 0x18 | 0x28  | 0x38 | SAT       |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             | S                                    | SAT           |            |              |             |  |

| 0x09 | 0x19 | 0x29  | 0x39 | CONT      |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             | C                                    | TNC           |            |              |             |  |

| 0x0A | 0x1A | 0x2A  | 0x3A | BRT       |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             | Е                                    | RT            |            |              |             |  |

| 0x0B | 0x1B | 0x2B  | 0x3B | LUMCON    | YBWI         | COMBMD YPEAK_MD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |                                      |               | YPEAI      | K_GN         |             |  |

| 0x0C | 0x1C | 0x2C  | 0x3C | COLRCON   | 0            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CK          | CKILL CTI_GN                         |               |            |              |             |  |

| 0x0D | 0x1D | 0x2D  | 0x3D | CH_CON    | 0            | BGND_EN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | BGND_COLR   | _COLR ANA_SW SW_RESET DUAL_CH SEL_CH |               |            | _CH          |             |  |

| 0x0E | 0x1E | 0x2E  | 0x3E | ANA_FIL   | 0            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0           | 1                                    | 1 0 0 1       |            |              |             |  |

Note: \* Read only registers

| Add     | dress      |             | DITT     | DITO      | DITE      | DITA      | DITO       | DITO      | DITA      | DITO      |

|---------|------------|-------------|----------|-----------|-----------|-----------|------------|-----------|-----------|-----------|

| CH1 CH2 | CH3 CH4    | Mnemonic    | BIT7     | BIT6      | BIT5      | BIT4      | BIT3       | BIT2      | BIT1      | BIT0      |

| 0:      | x40        | DET_SYNC *  | FLD4*    | FLD3*     | FLD2*     | FLD1*     | VAV4*      | VAV3*     | VAV2*     | VAV1*     |

| 0:      | x41        | PEAKAGC1    | WPEA     | K_MD4     | WPEA      | K_MD3     | WPEA       | K_MD2     | WPEA      | K_MD1     |

| 0:      | x42        | PEAKAGC2    | Cl       | HID       | WPEA      | K_REF     | WPEA       | K_RNG     | WPEA      | K_TIME    |

| 0:      | x43        | MISC        | OE       | AUTO_BGND | LIM16     | NOVID_656 | CLKN_OEB   | CLKP_OEB  | CLKN_MD   | CLKP_MD   |

| 0:      | x44        | AGC TIME    | 0        | 1         | 0 0       |           | GNTIME     |           | OST       | TIME      |

| 0:      | x45        | HSWIDTH     | 1        | 0         |           |           | HSW        | IDTH      |           |           |

| 0:      | x46        | SYNCPOL     | FLDN     | MODE      | VSMODE    | FLDPOL    | HSPOL      | VSPOL     | 1         | 0         |

| 0:      | x47        | CFILTER     | IFC      | OMP       | CL        | .PF       | ACC.       | TIME      | APC       | TIME      |

| 0:      | x48        | CDEL        | 0        | 1         | C_C       | ORE       | 0          |           | CDEL      |           |

| 0:      | x49        | U_GAIN      |          |           |           | U_0       | GAIN       |           |           |           |

| 0)      | (4A        | V_GAIN      |          |           |           | V_0       | GAIN       |           |           |           |

| 0)      | (4B        | U_OFF       |          |           |           | U_        | OFF        |           |           |           |

| 0>      | (4C        | V_OFF       |          |           |           | V_        | V_OFF      |           |           |           |

| 0>      | (4D        | CLK_MD      |          | CLKN      | I_DEL     |           |            | CLKP.     | _DEL      |           |

| 0)      | <b>4</b> Ε | CLK_DEL1    | GPP_VAL2 |           | MPP_MODE2 |           | GPP_VAL1   |           | MPP_MODE1 |           |

| 02      | κ4F        | CLK_DEL2    | GPP_VAL4 |           | MPP_MODE4 |           | GPP_VAL3   |           | MPP_MODE3 |           |

| 0:      | x50        | ADC_PWDN    | 0        | 0         | 1         | 1         | ADC_PWDN4  | ADC_PWDN3 | ADC_PWDN2 | ADC_PWDN1 |

| 0:      | x51        | NOVID_MD    | 0        | 0         | 0         | 0         | NOVII      | D_MD      | 1         | 1         |

| 0:      | x52        | RESERVED    | 0        | 0         | 0         | 0         | 0          | 1         | 0         | 1         |

| 0:      | x53        | RESERVED    | 0        | 0         | 0         | 0         | 0          | 0         | 0         | 0         |

| 0:      | x54        | RESERVED    | 0        | 0         | 0         | 0         | 0          | 0         | 0         | 0         |

| 0:      | x55        | RESERVED    | 1        | 0         | 0         | 0         | 0          | 0         | 0         | 0         |

| 0:      | x56        | RESERVED    | 0        | 0         | 0         | 0         | 0          | 1         | 1         | 0         |

| 0:      | x57        | RESERVED    | 0        | 0         | 0         | 0         | 0          | 0         | 0         | 0         |

| 0:      | x58        | DEV_ID *    | 0        | 1         | 0         | 0         | 0          | 0         | 0         | 0         |

| 0:      | x59        | DEV_ID *    | 0        | 0         | 1         | 0         | 0          | 0 0       |           | 0         |

| 0)      | (5A        | VDET_STATE* |          |           |           |           | VDET_STATE |           |           |           |

| 0)      | (5B        | VDET_ENA    | 0        | 0         | 0         | 0         | VDET_ENA   |           |           |           |

| 0>      | (5C        | VDET_MODE   | IRQENA   | IRQPOL    | 1         | 0         | 0          | 0         | VDET_     | _MODE     |

Note: \* Read only registers

| Address CH1 CH2 CH3 CH4 | Mnemonic | BIT7     | BIT6     | BIT5      | BIT4 | BIT3     | BIT2     | BIT1     | BIT0     |

|-------------------------|----------|----------|----------|-----------|------|----------|----------|----------|----------|

| 0x60                    | RESERVED | 0        | 0        | 0         | 0    | 0        | 0        | 0        | 0        |

| 0x61                    | RESERVED | 0        | 0        | 0         | 0    | 0        | 0        | 0        | 0        |

| 0x62                    | RESERVED | 0        | 0        | 0         | 0    | 0        | 0        | 0        | 0        |

| 0x63                    | RESERVED | 0        | 0        | 0         | 0    | 0        | 0        | 0        | 0        |

| 0x64                    | RESERVED | 0        | 0        | 0         | 0    | 0        | 0        | 0        | 0        |

| 0x65                    | RESERVED | 0        | 0        | 0         | 0    | 0        | 0        | 0        | 0        |

| 0x66                    | RESERVED | 0        | 0        | 0         | 0    | 0        | 0        | 0        | 0        |

| 0x67                    | RESERVED | 0        | 0        | 0         | 0    | 0        | 0        | 0        | 0        |

| 0x68                    | RESERVED | 0        | 0        | 0         | 0    | 0        | 0        | 0        | 0        |

| 0x69                    | RESERVED | 0        | 0        | 0         | 0    | 0        | 0        | 0        | 0        |

| 0x6A                    | RESERVED | 0        | 0        | 0         | 0    | 0        | 0        | 0        | 0        |

| 0x6B                    | RESERVED | 0        | 0        | 0         | 0    | 0        | 0        | 0        | 0        |

| 0x6C                    | RESERVED | 0        | 0        | 0         | 0    | 0        | 0        | 0        | 0        |

| 0x6D                    | RESERVED | 0        | 0        | 0         | 0    | 0        | 0        | 0        | 0        |

| 0x6E                    | RESERVED | 0        | 0        | 0         | 0    | 0        | 0        | 0        | 0        |

| 0x6F                    | RESERVED | 0        | 0        | 0         | 0    | 0        | 0        | 0        | 0        |

| 0x70                    | RESERVED | 0        | 0        | 0         | 0    | 0        | 0        | 0        | 0        |

| 0x71                    | CIF_MODE | HSCL_LPF | VSCL_ENA | VSCL_SYNC | 0    | 0        | 0        | 0        | 0        |

| 0x72                    | RESERVED | 0        | 0        | 0         | 0    | 0        | 0        | 0        | 0        |

| 0x73                    | RESERVED | 0        | 0        | 0         | 0    | 0        | 0        | 0        | 0        |

| 0x74                    | RESERVED | 0        | 0        | 0         | 0    | 0        | 0        | 0        | 0        |

| 0x75                    | CIF_54M  | 0        | 0        | 0         | 0    | CIF_54M4 | CIF_54M3 | CIF_54M2 | CIF_54M1 |

Page 28 of 65

Note: \* Read only registers

### **Recommended Value**

|      | Addı | ress           |      |            |       |     |              |

|------|------|----------------|------|------------|-------|-----|--------------|

| CH1  | CH2  | CH3            | CH4  | Mnemonic   | NTSC  | PAL | Non-realtime |

| 0x00 | 0x10 | 0x20           | 0x30 | VIDSTAT *  | 8'h00 |     |              |

| 0x01 | 0x11 | 0x21           | 0x31 | FORMAT     | C8    | 88  |              |

| 0x02 | 0x12 | 0x22           | 0x32 | HDELAY     | 20    |     |              |

| 0x03 | 0x13 | 0x23           | 0x33 | HACTIVE    | D0    |     |              |

| 0x04 | 0x14 | 0x24           | 0x34 | VDELAY     | 06    | 05  |              |

| 0x05 | 0x15 | 0x25           | 0x35 | VACTIVE    | F0    | 20  |              |

| 0x06 | 0x16 | 0x26           | 0x36 | MSB_ACTV   | 08    | 28  |              |

| 0x07 | 0x17 | 0x27           | 0x37 | HUE        | 80    |     |              |

| 0x08 | 0x18 | 0x28           | 0x38 | SAT        | 80    |     |              |

| 0x09 | 0x19 | 0x29           | 0x39 | CONT       | 80    |     |              |

| 0x0A | 0x1A | 0x2A           | 0x3A | BRT        | 80    |     |              |

| 0x0B | 0x1B | 0x2B           | 0x3B | LUMCON     | 02    | 82  |              |

| 0x0C | 0x1C | 0x2C           | 0x3C | COLRCON    | 06    |     |              |

| 0x0D | 0x1D | 0x2D           | 0x3D | OUTFMT     | 00    |     |              |

| 0x0E | 0x1E | 0x2E           | 0x3E | RESERVED   | 11    |     |              |

|      | 0x4  | 40             |      | DET_SYNC * | 00    |     |              |

|      | 0x4  | 41             |      | PEAKAGC1   | 00    |     |              |

|      | 0x4  | 42             |      | PEAKAGC2   | 00    |     |              |

|      | 0x4  | 43             |      | MISC       | C0    |     |              |

|      | 0x4  | 44             |      | AGCTIME    | 45    |     | 4F           |

|      | 0x4  | 45             |      | HSWIDTH    | A0    |     |              |

|      | 0x4  | 46             |      | SYNCPOL    | D0    |     | 10           |

|      | 0x4  | 47             |      | CFILTER    | 2F    |     |              |

|      | 0x4  | 48             |      | CDEL       | 64    |     |              |

|      | 0x4  | 49             |      | U_GAIN     | 80    |     |              |

|      | 0x4  | 1A             |      | V_GAIN     | 80    |     |              |

|      | 0x4  | 4B             |      | U_OFF      | 82    |     |              |

|      | 0x4  | <del>1</del> C |      | V_OFF      | 82    |     |              |

|      | 0x4  | 1D             |      | CLK_CON    | 80    |     |              |

|      | 0x4  | 4E             |      | MPP_MODE1  | 00    |     |              |

|      | 0x4  | 4F             |      | MPP_MODE2  | 00    |     |              |

|      | 0x   | 50             |      | ADC_PWDN   | 30    |     |              |

|      | 0x   | 51             |      | NOVID_MD   | 0F    |     | 00           |

|      | 0x   | 52             |      | RESERVED   | 05    |     |              |

|      | 0x   | 53             |      | RESERVED   | 00    |     |              |

|      | 0x   | 54             |      | RESERVED   | 00    |     |              |

|      | 0x:  | 55             |      | RESERVED   | 80    |     | 88           |

|      | 0x:  | 56             |      | RESERVED   | 06    |     |              |

|      | 0x   | 57             |      | RESERVED   | 00    |     |              |

|      | 0x   |                |      | DEV_ID *   | 40    |     |              |

|      | 0x   |                |      | DEV_ID *   | 20    |     |              |

|      | 0x   | 5A             |      | STATE_DET  | 00    |     |              |

|      | 0x   |                |      | VDET_ENA   | 0F    |     |              |

|      | 0x5C |                |      | DET_MODE   | 00    |     |              |

|      | 0x0  |                |      | RESERVED   | 00    |     |              |

|      | 0x0  |                |      | RESERVED   | 00    |     |              |

|      | 0x(  | 62             |      | RESERVED   | 00    |     |              |

|      | 0x0  | 63             |      | RESERVED   | 00    |     |              |