## ISL98003

8-Bit Video Analog Front End (AFE) with Measurement and Auto-Adjust Features

FN6760 Rev 0.00 September 25, 2008

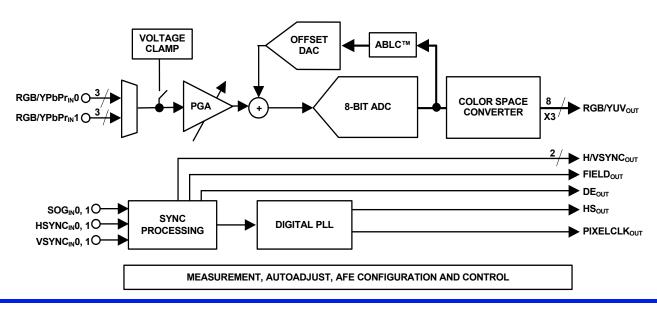

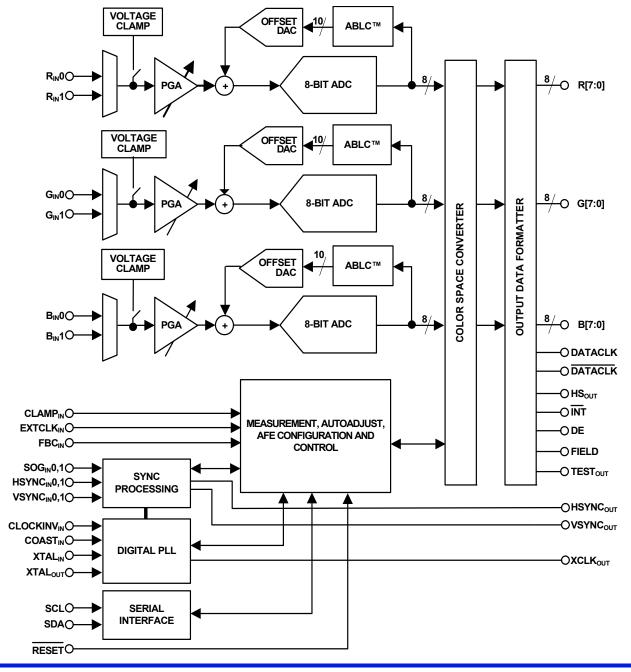

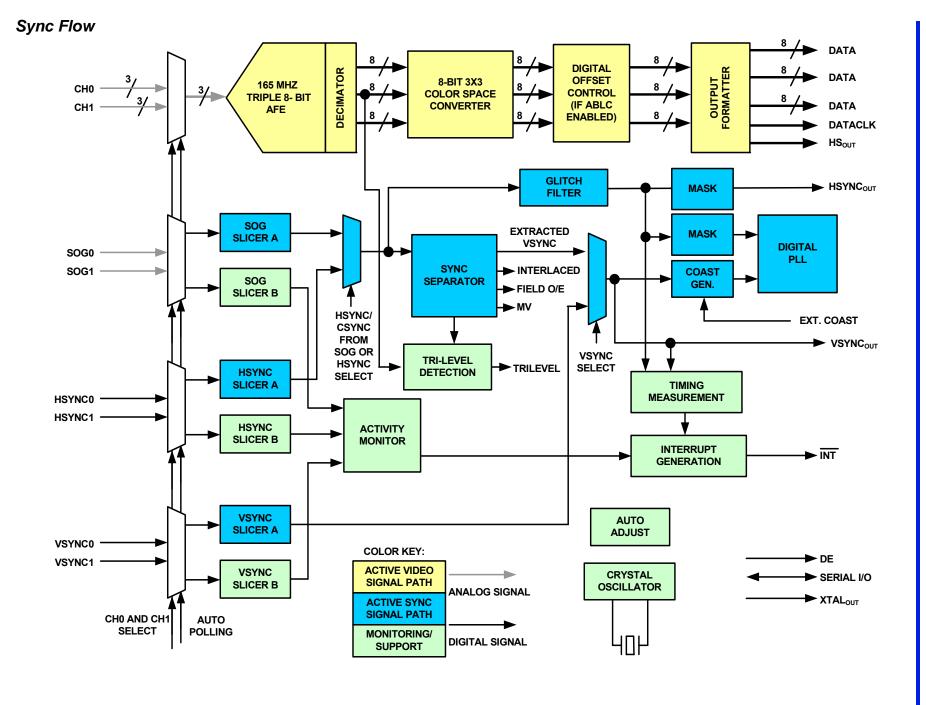

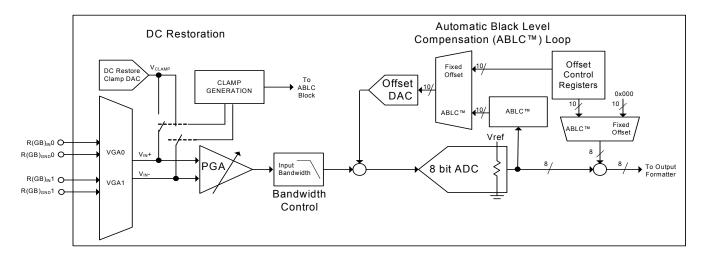

The ISL98003 3-channel, 8-bit Analog Front End (AFE) contains all the functionality needed to digitize analog YPbPr video from HDTV tuners, set-top boxes, SD and HD DVDs, as well as RGB graphics signals from personal computers and workstations. The fourth generation analog design delivers 8-bit performance and a 165MSPS maximum conversion rate supporting resolutions up to UXGA at 60Hz. The front end's programmable input bandwidth ensures sharp, low noise images at all resolutions.

To accelerate and simplify mode detection, the ISL98003 integrates a sophisticated set of measurement tools that fully characterizes the video signal and timing, offloading the host microcontroller. Automatic Black Level Compensation (ABLC™) eliminates part-to-part offset variation, ensuring perfect black level performance in every application.

The ISL98003's Digital PLL generates a pixel clock from the analog source's HSYNC or SOG (Sync-On-Green) signals. Pixel clock output frequencies range from 10MHz to 165MHz with sampling clock jitter of 250ps peak-to-peak.

## **Applications**

- · Flat Panel TVs

- · Front/Rear Projection TVs

- · PC LCD Monitors and Projectors

- · High Quality Scan Converters

- · Video/Graphics Processing

## Simplified Block Diagram

#### **Features**

- 8-Bit Triple Analog-to-Digital Converters with Oversampling Up to 8x in Video Modes

- · Fast Automatic Selection of Best Sampling Phase

- 165MSPS Maximum Conversion Rate (ISL98003CNZ-165)

- Robust, Glitchless Macrovision™-Compliant Sync Separator

- · Analog VCR "Trick Mode" Support

- · ABLC for Perfect Black Level Performance

- · 2-Channel Input Multiplexer

- Precision Sync Timing Measurement

- RGB to YUV Color Space Converter

- · Low PLL Clock Jitter (250ps Peak-to-Peak)

- Programmable Input Bandwidth (10MHz to 450MHz)

- · 64 Interpixel Sampling Positions

- · ±6dB Gain Adjustment Range

- · Pb-Free (RoHS compliant)

### Related Literature

Technical Brief TB363 "Guidelines for Handling and Processing Moisture Sensitive Surface Mount Devices (SMDs)".

## **Ordering Information**

| PART NUMBER/PART MARKING (Note) | TEMP. RANGE<br>(°C) | PACKAGE<br>(Pb-Free) | PKG.<br>DWG.# |

|---------------------------------|---------------------|----------------------|---------------|

| ISL98003INZ-110                 | -40 to +85          | 80 Ld EPTQFP         | Q80.12x12     |

| ISL98003CNZ-110                 | 0 to +70            | 80 Ld EPTQFP         | Q80.12x12     |

| ISL98003CNZ-150                 | 0 to +70            | 80 Ld EPTQFP         | Q80.12x12     |

| ISL98003CNZ-165                 | 0 to +70            | 80 Ld EPTQFP         | Q80.12x12     |

| ISL98003CNZ-EVALZ               | Evaluation Platform | ·                    |               |

NOTE: These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

## **Block Diagram**

#### **Absolute Maximum Ratings**

| $\begin{array}{llllllllllllllllllllllllllllllllllll$    |

|---------------------------------------------------------|

| Human Body Model (Per MIL-STD-883 Method 3015.7) 3000V  |

| Machine Model (Per EIAJ ED-4701 Method C-111)250V       |

| Charged Device Model (Per EOS/ESD DS5.3, 4/14/93) 1200V |

#### **Thermal Information**

| Thermal Resistance (Typical Notes 1, 2) | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) |

|-----------------------------------------|------------------------|------------------------|

| EPTQFP Package                          | 28                     | 14                     |

| Maximum Power Dissipation               |                        | 1.2W                   |

| Maximum Junction Temperature            |                        | +125°C                 |

| Maximum Storage Temperature Range       | 65                     | °C to +150°C           |

| Pb-Free Reflow Profile                  |                        | ee link below          |

| http://www.intersil.com/pbfree/Pb-FreeF | Reflow.asp             |                        |

## **Operating Conditions**

| Temperature Range    |                      |

|----------------------|----------------------|

| ISL98003INZ          | 40°C to +85°C        |

| ISL98003CNZ          | 0°C to +70°C         |

| Supply Voltage Range | 3.3V ±10%, 1.8V ±10% |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 2. For  $\theta_{JC}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

### **Electrical Specifications**

Specifications apply for  $V_{A3.3} = V_{D3.3} = V_{PLLA3.3} = 3.3V$ ,  $V_{A1.8} = V_{D1.8} = V_{PLLD1.8} = V_{ADCD1.8} = 1.8V$ , pixel rate = 110MHz for ISL98003-110, 150MHz for ISL98003-150 and 165MHz for ISL98003-165,  $f_{XTAL} = 25$ MHz, and  $T_A = +25$ °C, unless otherwise specified.

| SYMBOL         | PARAMETER                                  | TEST LEVEL or NOTES                 | MIN<br>(Note 6) | TYP   | MAX<br>(Note 6) | UNITS |

|----------------|--------------------------------------------|-------------------------------------|-----------------|-------|-----------------|-------|

| FULL CHANNE    | L CHARACTERISTICS                          |                                     |                 |       |                 |       |

|                | Conversion Rate                            |                                     |                 |       |                 |       |

|                | ISL98003-110                               |                                     | 10              |       | 110             | MHz   |

|                | ISL98003-150                               |                                     | 10              |       | 150             | MHz   |

|                | ISL98003-165                               |                                     | 10              |       | 165             | MHz   |

|                | ADC Resolution                             |                                     | 8               |       |                 | Bits  |

|                | Missing Codes                              | Guaranteed monotonic                |                 |       | None            |       |

| DNL            | Differential Non-Linearity                 | (Note 3)                            |                 |       |                 |       |

| (Full-Channel) | ISL98003-110                               |                                     | -0.9            | ±0.3  | +1.0            | LSB   |

|                | ISL98003-150                               |                                     | -0.9            | ±0.35 | +1.0            | LSB   |

|                | ISL98003-165                               |                                     | -0.9            | ±0.4  | +1.0            | LSB   |

| INL            | Integral Non-Linearity                     | (Note 3)                            |                 |       |                 |       |

| (Full-Channel) | ISL98003-110                               |                                     |                 | ±0.5  | ±2.75           | LSB   |

|                | ISL98003-150                               |                                     |                 | ±0.6  | ±3.25           | LSB   |

|                | ISL98003-165                               |                                     |                 | ±0.7  | ±3.25           | LSB   |

|                | Gain Adjustment Range                      |                                     |                 | ±6    |                 | dB    |

|                | Gain Adjustment Resolution                 |                                     |                 | 10    |                 | Bits  |

|                | Gain Matching Between<br>Channels          | Percent of full scale               |                 | ±2    |                 | %     |

|                | Full Channel Offset Error,<br>ABLC Enabled | ADC LSBs, over time and temperature |                 | ±0.5  | ±1.0            | LSB   |

## **Electrical Specifications**

Specifications apply for  $V_{A3.3} = V_{D3.3} = V_{PLLA3.3} = 3.3V$ ,  $V_{A1.8} = V_{D1.8} = V_{PLLD1.8} = V_{ADCD1.8} = 1.8V$ , pixel rate = 110MHz for ISL98003-110, 150MHz for ISL98003-150 and 165MHz for ISL98003-165,  $f_{XTAL} = 25$ MHz, and  $T_A = +25$ °C, unless otherwise specified. (**Continued**)

| SYMBOL                           | PARAMETER                                                | TEST LEVEL or NOTES                                                                  | MIN<br>(Note 6)      | ТҮР        | MAX<br>(Note 6) | UNITS            |

|----------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------|------------|-----------------|------------------|

|                                  | Offset Adjustment Range<br>(ABLC Enabled or Disabled)    | (see "Automatic Black Level<br>Compensation (ABLC™) and Gain<br>Control" on page 21) |                      | ±50%       |                 | ADC<br>Fullscale |

| ANALOG VIDE                      | O INPUT CHARACTERISTICS (R                               | <sub>IN</sub> 0-1, G <sub>IN</sub> 0-1, B <sub>IN</sub> 0-1)                         |                      | •          |                 |                  |

|                                  | Input Range                                              |                                                                                      | 0.35                 | 0.7        | 1.4             | V <sub>P-P</sub> |

|                                  | Input Bias Current                                       | DC-restore clamp off                                                                 |                      | ±0.01      | ±1              | μA               |

|                                  | Input Capacitance                                        |                                                                                      |                      | 5          |                 | pF               |

|                                  | Full Power Bandwidth                                     | Programmable                                                                         |                      | 10 to 450  |                 | MHz              |

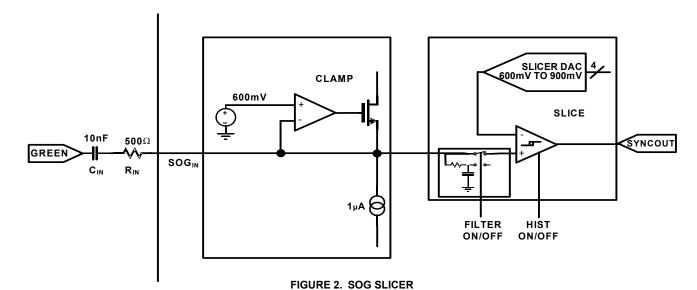

| SOG INPUT CI                     | HARACTERISTICS (SOG <sub>IN</sub> 0-1)                   |                                                                                      |                      | 1          |                 |                  |

|                                  | Sync Tip Clamp                                           |                                                                                      |                      | 600        |                 | mV               |

|                                  | SOG Pull-Down                                            |                                                                                      |                      | 1          |                 | μA               |

| V <sub>IH</sub> /V <sub>IL</sub> | Input Threshold Voltage (Relative to Bottom of Sync Tip) | Programmable (see "Register Listing" on page 10)                                     |                      | 0 to 0.3   |                 | V                |

|                                  | Input Capacitance                                        |                                                                                      |                      | 5          |                 | pF               |

| HSYNC INPUT                      | CHARACTERISTICS (HSYNCINO                                | I-1)                                                                                 |                      |            | 1               | -                |

| V <sub>IH</sub> /V <sub>IL</sub> | Input Threshold Voltage                                  | Programmable (see "Register Listing" on page 10)                                     |                      | 0.4 to 3.2 |                 | V                |

|                                  | Hysteresis                                               | Centered around threshold voltage                                                    |                      | 240        |                 | mV               |

| I                                | Input Leakage Current                                    |                                                                                      |                      | ±10        |                 | nA               |

| C <sub>IN</sub>                  | Input Capacitance                                        |                                                                                      |                      | 5          |                 | pF               |

| DIGITAL INPU                     | T CHARACTERISTICS (ALL DIGI                              | TAL INPUT PINS EXCEPT SCL, VSYN                                                      | C <sub>IN</sub> 0-1) |            | 1               | -                |

| V <sub>IH</sub>                  | Input High Voltage                                       |                                                                                      | 2.0                  |            |                 | V                |

| V <sub>IL</sub>                  | Input Low Voltage                                        |                                                                                      |                      |            | 0.8             | V                |

| I                                | Input Leakage Current                                    | $\overline{\text{RESET}}$ has a 65k $\Omega$ pull-up to VD3.3                        |                      | ±10        |                 | nA               |

| C <sub>IN</sub>                  | Input Capacitance                                        |                                                                                      |                      | 5          |                 | pF               |

| SCHMITT DIGI                     | TAL INPUT CHARACTERISTICS                                | (SCL, VSYNC <sub>IN</sub> 0-3)                                                       |                      |            |                 |                  |

| V <sub>T</sub> +                 | Low to High Threshold Voltage                            |                                                                                      | 1.45                 |            |                 | V                |

| V <sub>T</sub> -                 | High to Low Threshold Voltage                            |                                                                                      |                      |            | 0.95            | V                |

| 1                                | Input Leakage Current                                    |                                                                                      |                      | ±10        |                 | nA               |

| C <sub>IN</sub>                  | Input Capacitance                                        |                                                                                      |                      | 5          |                 | pF               |

| DIGITAL OUTP                     | PUT CHARACTERISTICS (ALL O                               | JTPUT PINS EXCEPT INT AND SDA)                                                       |                      | !          | !               | <del>'</del>     |

| V <sub>OH</sub>                  | Output HIGH Voltage, I <sub>O</sub> = 8mA                |                                                                                      | 2.4                  |            |                 | V                |

| V <sub>OL</sub>                  | Output LOW Voltage, I <sub>O</sub> = -8mA                |                                                                                      |                      |            | 0.4             | V                |

| DIGITAL OUTP                     | PUT CHARACTERISTICS (INT)                                |                                                                                      |                      |            | 1               | -                |

| V <sub>OL</sub>                  | Output LOW Voltage, I <sub>O</sub> = -8mA                | Open-drain, with 65k $\Omega$ pull-up to V $_{D3.3}$                                 |                      |            | 0.4             | V                |

| DIGITAL OUTF                     | PUT CHARACTERISTICS (SDA)                                |                                                                                      |                      | 1          | 1               | _1               |

| V <sub>OL</sub>                  | Output LOW Voltage, I <sub>O</sub> = -4mA                | Open-drain                                                                           |                      |            | 0.4             | V                |

| POWER SUPP                       | LY REQUIREMENTS                                          |                                                                                      |                      | 1          | 1               |                  |

| V <sub>A3.3</sub>                | Analog Supply Voltage, 3.3V                              | Includes VPLL <sub>A3.3</sub>                                                        | 3.0                  | 3.3        | 3.6             | V                |

### **Electrical Specifications**

Specifications apply for  $V_{A3.3} = V_{D3.3} = V_{PLLA3.3} = 3.3V$ ,  $V_{A1.8} = V_{D1.8} = V_{PLLD1.8} = V_{ADCD1.8} = 1.8V$ , pixel rate = 110MHz for ISL98003-110, 150MHz for ISL98003-150 and 165MHz for ISL98003-165,  $f_{XTAL} = 25$ MHz, and  $T_A = +25$ °C, unless otherwise specified. (**Continued**)

| SYMBOL               | PARAMETER                                   | TEST LEVEL or NOTES                                  | MIN<br>(Note 6) | TYP  | MAX<br>(Note 6) | UNITS  |

|----------------------|---------------------------------------------|------------------------------------------------------|-----------------|------|-----------------|--------|

| V <sub>A1.8</sub>    | Analog Supply Voltage, 1.8V                 |                                                      | 1.65            | 1.8  | 2.0             | V      |

| V <sub>D3.3</sub>    | Digital Supply Voltage, 3.3V                |                                                      | 3.0             | 3.3  | 3.6             | ٧      |

| V <sub>D1.8</sub>    | Digital Supply Voltage, 1.8V                | Includes VADC <sub>D1.8</sub> , VPLL <sub>D1.8</sub> | 1.65            | 1.8  | 2.0             | V      |

| I <sub>A3.3</sub>    | Analog Supply Current, 3.3V (Note 4)        |                                                      |                 | 40   | 90              | mA     |

| IPLL <sub>A3.3</sub> |                                             |                                                      |                 | 14   | 25              | mA     |

| I <sub>A1.8</sub>    | Analog Supply Current, 1.8V (Note 4)        | Includes 1.8V ADC reference current draw             |                 | 280  | 375             | mA     |

| I <sub>D3.3</sub>    | Digital Supply Current, 3.3V (Note 4)       | Grayscale ramp input                                 |                 | 40   | 60              | mA     |

| I <sub>D1.8</sub>    | Digital Supply Current, 1.8V                | Grayscale ramp input                                 |                 | 65   | 95              | mA     |

| IADC <sub>D1.8</sub> | (Note 4)                                    |                                                      |                 | 33   | 65              | mA     |

| IPLL <sub>D1.8</sub> |                                             |                                                      |                 | 1.8  | 10              | mA     |

| P <sub>D</sub>       | Total Power Dissipation                     | Grayscale ramp input                                 |                 | 0.95 | 1.1             | W      |

|                      |                                             | Standby Mode                                         |                 | 50   | 100             | mW     |

| C TIMING C           | HARACTERISTICS                              |                                                      |                 |      |                 |        |

|                      | PLL Jitter (Note 5)                         |                                                      |                 | 250  | 450             | ps p-p |

|                      | Sampling Phase Steps                        | 5.6° per step                                        |                 | 64   |                 |        |

|                      | Sampling Phase Tempco                       |                                                      |                 | ±1   |                 | ps/°C  |

|                      | Sampling Phase<br>Differential Nonlinearity | Degrees out-of-phase +360°                           |                 | ±3   |                 | 0      |

|                      | HSYNC Frequency Range                       |                                                      | 10              |      | 150             | kHz    |

| f <sub>XTAL</sub>    | Crystal Frequency Range                     |                                                      | 12              | 25   | 27              | MHz    |

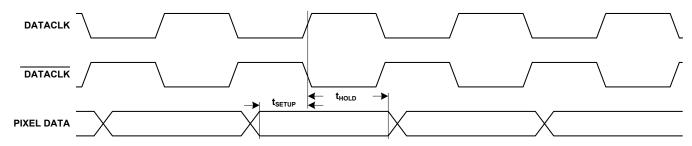

| <sup>t</sup> SETUP   | Data Valid Before Rising Edge of DATACLK    | 20pF DATACLK load,<br>20pF DATA load                 | 1.8             |      |                 | ns     |

| t <sub>HOLD</sub>    | Data Valid After Rising Edge of DATACLK     | 20pF DATACLK load,<br>20pF DATA load                 | 3.4             |      |                 | ns     |

#### NOTES:

- 3. Linearity tested at room temperature and established across commercial temperature range by correlation to characterization.

- 4. Supply current specified at max pixel rate (165MHz) with gray scale video applied.

- 5. Jitter tested at rated frequencies (110MHz, 150MHz and 165MHz) and at minimum frequency (10MHz).

- 6. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

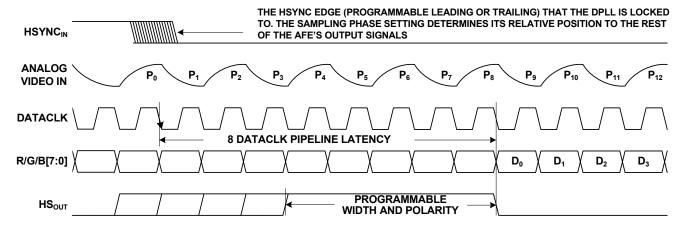

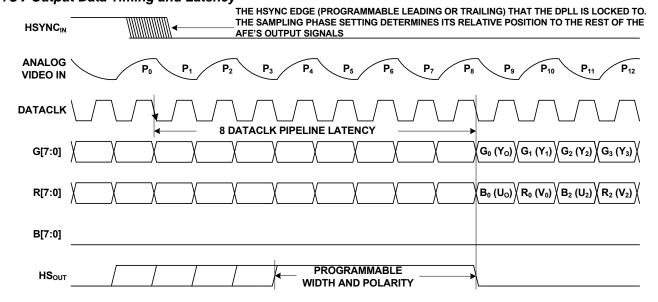

## **Timing Diagrams**

## **Data Output Setup and Hold Timing**

## RGB Output Data Timing and Latency

### YUV Output Data Timing and Latency

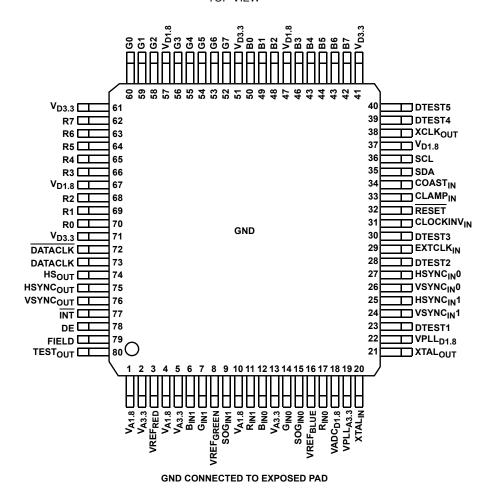

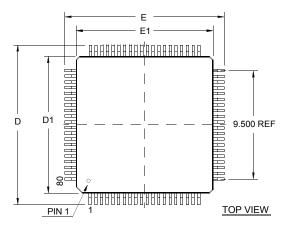

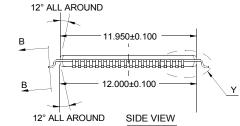

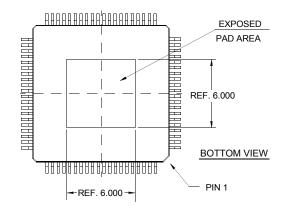

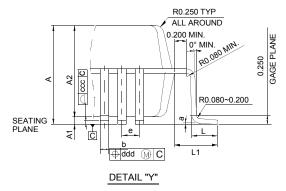

### **Pinout**

#### ISL98003 (80 LD EPTQFP) TOP VIEW

## Pin Descriptions

| SYMBOL                                                                   | DESCRIPTION                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R <sub>IN</sub> 0, 1                                                     | Analog inputs. Red channels. AC-couple through 0.1µF.                                                                                                                                                                                                                                                                                  |

| G <sub>IN</sub> 0, 1                                                     | Analog inputs. Green channels. AC-couple through 0.1µF.                                                                                                                                                                                                                                                                                |

| B <sub>IN</sub> 0, 1                                                     | Analog inputs. Blue channels. AC-couple through 0.1µF.                                                                                                                                                                                                                                                                                 |

| VREF <sub>RED</sub> ,<br>VREF <sub>GREEN</sub> ,<br>VREF <sub>BLUE</sub> | Analog inputs. Reference voltage for ADCs. Tie to 1.8V reference voltage ( $V_{A1.8}$ is acceptable if low noise). Decouple with 0.1 $\mu$ F capacitor to GND <sub>A</sub> .                                                                                                                                                           |

| SOG <sub>IN</sub> 0, 1                                                   | Analog inputs. Sync on Green. Connect to corresponding Green channel video source through a $0.01\mu F$ capacitor in series with a $500\Omega$ resistor.                                                                                                                                                                               |

| HSYNC <sub>IN</sub> 0, 1                                                 | Digital <i>high impedance</i> 3.3V inputs with 240mV hysteresis. Connect to corresponding channel's HSYNC source. For 5V signals divide input with a 1k/1.9k divider. Place the divider as close as possible to the device pin. Place a 50pF capacitor in parallel with the 1k resistor to reduce the filtering effect of the divider. |

| VSYNC <sub>IN</sub> 0, 1                                                 | Digital <i>high impedance</i> 3.3V inputs with 240mV hysteresis. Connect to corresponding channel's VSYNC source. For 5V signals divide input with a 1k/1.9k divider. Place the divider as close as possible to the device pin. Place a 50pF capacitor in parallel with the 1k resistor to reduce the filtering effect of the divider. |

| COAST <sub>IN</sub>                                                      | Digital 3.3V input. When this input is high and external COAST is selected, the PLL will coast, ignoring all transitions on the active channel's HSYNC/SOG.                                                                                                                                                                            |

## Pin Descriptions (Continued)

| SYMBOL               | DESCRIPTION                                                                                                                                                                                                                                    |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLAMP <sub>IN</sub>  | Digital 3.3V input. When this input is high and external CLAMP is selected, connects the selected channels inputs to the clamp DAC.                                                                                                            |

| CLOCKINVIN           | Digital 3.3V input. When high, changes the pixel sampling phase by 180°. Toggle at frame rate during VSYNC to allow 2x undersampling to sample odd and even pixels on sequential frames. Tie to D <sub>GND</sub> if unused.                    |

| TEST <sub>OUT</sub>  | 3.3V digital output. A delayed version of internal COAST or CLAMP when selected.                                                                                                                                                               |

| RESET                | Digital 3.3V input, active low, $70k\Omega$ pull-up to $V_D$ . Take low for at least 1 $\mu$ s and then high again to reset the ISL98003. This pin is not necessary for normal use and may be tied directly to the $V_D$ supply.               |

| XTAL <sub>IN</sub>   | Analog input. Connect to external 12MHz to 27MHz crystal and load capacitor (see crystal spec for recommended loading). Typical oscillation amplitude is 1.0V <sub>P-P</sub> centered around 0.5V.                                             |

| XTAL <sub>OUT</sub>  | Analog output. Connect to external 12MHz to 27MHz crystal and load capacitor (see crystal spec for recommended loading). Typical oscillation amplitude is 1.0V <sub>P-P</sub> centered around 0.5V.                                            |

| XCLK <sub>OUT</sub>  | 3.3V digital output. Buffered crystal clock output at f <sub>XTAL</sub> or f <sub>XTAL</sub> /2. May be used as system clock for other system components.                                                                                      |

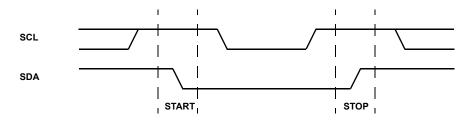

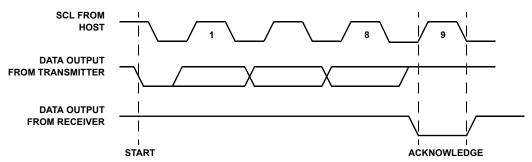

| SCL                  | Digital input, 5V tolerant, 500mV hysteresis. Serial data clock for 2-wire interface.                                                                                                                                                          |

| SDA                  | Bidirectional Digital I/O, open drain, 5V tolerant. Serial data I/O for 2-wire interface.                                                                                                                                                      |

| EXTCLK <sub>IN</sub> | Digital 3.3V input. External clock input for AFE.                                                                                                                                                                                              |

| R[7:0]               | 3.3V digital output. 8-bit Red channel pixel data.                                                                                                                                                                                             |

| G[7:0]               | 3.3V digital output. 8-bit Green channel pixel data.                                                                                                                                                                                           |

| B[7:0]               | 3.3V digital output. 8-bit Blue channel pixel data.                                                                                                                                                                                            |

| DATACLK              | 3.3V digital output. Data (pixel) clock output.                                                                                                                                                                                                |

| DATACLK              | 3.3V digital output. Inverse of DATACLK.                                                                                                                                                                                                       |

| HS <sub>OUT</sub>    | 3.3V digital output. HSYNC output aligned with pixel data. Use this output to frame the digital output data. This output is always purely horizontal sync (without any composite sync signals).                                                |

| HSYNC <sub>OUT</sub> | 3.3V digital output. Buffered HSYNC (or SOG or CSYNC) output. This is typically used for measuring HSYNC period. This output will pass composite sync signals and Macrovision signals if present on HSYNC <sub>IN</sub> or SOG <sub>IN</sub> . |

| VSYNC <sub>OUT</sub> | 3.3V digital output. Buffered VSYNC output. For composite sync signals, this output will be asserted for the duration of the disruption of the normal HSYNC pattern. This is typically used for measuring VSYNC period.                        |

| ĪNT                  | Digital output, open drain, 5V tolerant. Interrupt output indicating mode change or command execution status. Pull high with a 4.7k resistor.                                                                                                  |

| DE                   | 3.3V digital output. High when there is valid video data, low during horizontal and vertical blanking periods.                                                                                                                                 |

| FIELD                | 3.3V digital output. For interlaced video, this output will changes states to indicate whether current field is even or odd. Polarity is determined by configuration register.                                                                 |

| V <sub>A3.3</sub>    | Power supply for the analog section. Connect to a 3.3V supply and bypass each pin to GND with 0.1µF.                                                                                                                                           |

| V <sub>A1.8</sub>    | Power supply for the analog section. Connect to a 1.8V supply and bypass each pin to GND with 0.1µF.                                                                                                                                           |

| VPLL <sub>A3.3</sub> | Power supply for the analog PLL section. Connect to a 3.3V supply and bypass to GND with 0.1µF.                                                                                                                                                |

| GND                  | Ground return connected to exposed pad.                                                                                                                                                                                                        |

| V <sub>D3.3</sub>    | Power supply for all digital I/Os. Connect to a 3.3V supply and bypass each pin to GND with 0.1µF.                                                                                                                                             |

| V <sub>D1.8</sub>    | Power supply for digital core logic. Connect to a 1.8V supply and bypass each pin to GND with 0.1µF.                                                                                                                                           |

| VADC <sub>D1.8</sub> | Power supply for the digital ADC section. Connect to a 1.8V supply and bypass to GND with 0.1µF.                                                                                                                                               |

| VPLL <sub>D1.8</sub> | Power supply for the digital PLL section. Connect to a 1.8V supply and bypass to GND with 0.1µF.                                                                                                                                               |

| TEST1, 2, 3, 4, 5    | For production use only. Tie to GND.                                                                                                                                                                                                           |

## Register Listing

| ADDRESS    | REGISTER<br>(DEFAULT VALUE)                            | BITS | FUNCTION NAME               | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|------------|--------------------------------------------------------|------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| STATUS AND | STATUS AND INTERRUPT REGISTERS                         |      |                             |                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 0x01       | Selected Input Channel<br>Characteristics, (read only) | 1:0  | SYNC Type                   | 00: Automatic Sync Selection logic could not find good sync on H, V, or SOG (Automatic Sync mode only). 01: SYNC on HSYNC/VSYNC 10: CSYNC on HSYNC 11: CSYNC on Green Channel (SOG)                                                                                                                                                                                                                                                       |  |  |  |

|            |                                                        | 2    | HSYNC Polarity              | 0: HSYNC Active High 1: HSYNC Active Low                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|            |                                                        | 3    | VSYNC Polarity              | 0: VSYNC Active High 1: VSYNC Active Low                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|            |                                                        | 4    | Tri-level Sync              | 0: Bi-level SOG (if SOG is active) 1: Tri-level SOG                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|            |                                                        | 5    | Interlaced (Only for CSYNC) | Non-interlaced or progressive signal     Interlaced signal                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|            |                                                        | 6    | Macrovision                 | No Macrovision detected     Macrovision encoding detected                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|            |                                                        | 7    | PLL Locked                  | 0: PLL unlocked 1: PLL locked to incoming HSYNC                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 0x02       | CH0 and CH1 Activity<br>Status, (read only)            | 0    | HSYNC0 Activity             | 0: HSYNC0 Inactive 1: HSYNC0 Active – There is a periodic signal with frequency >1kHz and consistent low/high times on this input.                                                                                                                                                                                                                                                                                                        |  |  |  |

|            |                                                        | 1    | VSYNC0 Activity             | VSYNC0 Inactive     VSYNC0 Active – There is a periodic signal with frequency >20Hz and consistent low/high times on this input.                                                                                                                                                                                                                                                                                                          |  |  |  |

|            |                                                        | 3:2  | SOG0 Activity               | <ul> <li>00: SOG0 Inactive – No transitions detected at the SOG Slicer output.</li> <li>01: SOG0 Active – Non-periodic transitions detected at the SOG Slicer output – possibly valid SOG with a bad slicer threshold, or simply video with no valid SOG.</li> <li>10: SOG0 Periodic – There is a periodic signal with frequency &gt;1kHz and consistent low/high times on this input. This is most likely a valid SOG signal.</li> </ul> |  |  |  |

|            |                                                        | 4    | HSYNC1 Activity             | See HSYNC0 Activity description                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|            |                                                        | 5    | VSYNC1 Activity             | See VSYNC0 Activity description                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|            |                                                        | 7:6  | SOG1 Activity               | See SOG0 Activity description                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 0x03       | Not Used (read only)                                   | 7:0  | Not Used                    | Ignore                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| ADDRESS | REGISTER<br>(DEFAULT VALUE)                           | BITS      | FUNCTION NAME                       | DESCRIPTION                                                                                                                           |

|---------|-------------------------------------------------------|-----------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 0x04    | Interrupt Status,                                     | 0         | CH0 Sync Changed                    | No change     CH0 activity or polarity changed                                                                                        |

|         | Write a 1 to each bit to clear it, 0xFF to clear all. | 1         | CH1 Sync Changed                    | No change     CH1 activity or polarity changed                                                                                        |

|         |                                                       | 2         | N/A                                 | Ignore                                                                                                                                |

|         |                                                       | 3         | N/A                                 | Ignore                                                                                                                                |

|         |                                                       | 4         | Selected Input Channel<br>Disrupted | No change     Currently selected Input Channel's HSYNC or VSYNC signal has changed (fast notification of a mode change).              |

|         |                                                       | 5         | Selected Input Channel<br>Changed   | No change     Currently selected Input Channel's HSYNC or VSYNC period or pulse width has settled to a new value and can be measured. |

|         | 6                                                     | VSYNC INT | 0: Default state 1: VSYNC occurred  |                                                                                                                                       |

|         |                                                       | 7         | PADJ INT                            | Default state     Phase Adjustment function completed.                                                                                |

| 0x05    | Interrupt Mask Register,<br>(0xFF)                    | 0         | CH0 Mask                            | Generate interrupt if CH0 sync activity, polarity, period, or pulse width changes.     Mask CH0 interrupt                             |

|         |                                                       | 1         | CH1 Mask                            | Generate interrupt if CH1 sync activity, polarity, period, or pulse width changes.     Mask CH1 interrupt                             |

|         |                                                       | 2         | N/A                                 | Set to 1                                                                                                                              |

|         |                                                       | 3         | N/A                                 | Set to 1                                                                                                                              |

|         |                                                       | 4         | Input Disrupted Mask                | Generate interrupt if selected Input Channel's sync inputs are disrupted.     Mask Input Channel interrupt                            |

|         |                                                       | 5         | Input Changed Mask                  | Generate interrupt after selected Input Channel period or pulse width settles to new value.     Mask Input Channel interrupt          |

|         |                                                       | 6         | VSYNC INT Mask                      | Generate interrupt every VSYNC     Mask VSYNC Interrupt                                                                               |

|         |                                                       | 7         | PADJ INT Mask                       | Generate interrupt upon phase adjustment block request completion.     Mask Phase adjustment interrupt                                |

| ADDRESS                          | REGISTER<br>(DEFAULT VALUE)        | BITS                 | FUNCTION NAME                                                                              | DESCRIPTION                                                                                                                                                                                                                                                                                                |

|----------------------------------|------------------------------------|----------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CONFIGURA                        | ATION REGISTERS                    |                      |                                                                                            |                                                                                                                                                                                                                                                                                                            |

| 0x10 Input Configuration, (0x00) | 1:0                                | Input Channel Select | Sets video muxes as well as HSYNC, VSYNC, and SOG input muxes. 0: CH0 1: CH1 2: N/A 3: N/A |                                                                                                                                                                                                                                                                                                            |

|                                  |                                    | 2                    | N/A                                                                                        | Set to 0                                                                                                                                                                                                                                                                                                   |

|                                  |                                    | 3                    | DC Coupled Input Enable                                                                    | 0: AC-coupled Inputs 1: DC-coupled Inputs                                                                                                                                                                                                                                                                  |

|                                  |                                    | 4                    | RGB YUV                                                                                    | 0: RGB inputs (Clamp DAC = 300mV for R, G, B, half scale analog shift for R, G, and B, base ABLC target code = 0x00 for R, G, and B).  1: YPbPr inputs (Clamp DAC = 600mV for R and B, 300mV for G, half scale analog shift for G channel only, base ABLC target code = 0x00 for G, = 0x80 for R and B).   |

|                                  |                                    | 5                    | N/A                                                                                        | Set to 0                                                                                                                                                                                                                                                                                                   |

|                                  |                                    | 6                    | EXT Clamp SEL                                                                              | 0: Internal CLAMP generation 1: External CLAMP source                                                                                                                                                                                                                                                      |

|                                  |                                    | 7                    | EXT Clamp POL                                                                              | 0: Active high external CLAMP 1: Active low external CLAMP                                                                                                                                                                                                                                                 |

| 0x11                             | 0x11 Sync Source Selection, (0x00) | 0                    | Sync Select                                                                                | O: Automatic (HSYNC, VSYNC sources selected based on sync activity. Multiplexer settings chosen are displayed in the Input Characteristics register).  1: Manual (bits 1and 2 determine HSYNC and VSYNC source).                                                                                           |

|                                  |                                    | 1                    | HSYNC Source                                                                               | 0: HSYNC input pin<br>1: SOG                                                                                                                                                                                                                                                                               |

|                                  |                                    | 2                    | VSYNC Source                                                                               | 0: VSYNC input pin<br>1: Sync Separator output                                                                                                                                                                                                                                                             |

| 0x12                             | Red Gain MSB, (0x55)               | 7:0                  | Red Gain MSB                                                                               | Red channel gain, where: gain (V/V) = $0.5 + [9:0]/682$ MSB/LSB 0x00 00: gain = $0.5$ V/V ( $1.4$ V <sub>P-P</sub> input = full range of ADC) 0x55 00: gain = $1.0$ V/V ( $0.7$ V <sub>P-P</sub> input = full range of ADC) 0xFF C0: gain = $2.0$ V/V ( $0.35$ V <sub>P-P</sub> input = full range of ADC) |

| 0x13                             | Red Gain LSB, (0x00)               | 5:0                  | N/A                                                                                        |                                                                                                                                                                                                                                                                                                            |

|                                  |                                    | 7:6                  | Red Gain LSB                                                                               | 2 LSBs of 10-bit gain word                                                                                                                                                                                                                                                                                 |

| 0x14                             | Green Gain MSB, (0x55)             | 7:0                  | Green Gain MSB                                                                             | See Red Gain                                                                                                                                                                                                                                                                                               |

| 0x15                             | Green Gain LSB, (0x00)             | 5:0                  | N/A                                                                                        |                                                                                                                                                                                                                                                                                                            |

|                                  |                                    | 7:6                  | Green Gain LSB                                                                             | See Red Gain                                                                                                                                                                                                                                                                                               |

| 0x16                             | Blue Gain MSB, (0x55)              | 7:0                  | Blue Gain MSB                                                                              | See Red Gain                                                                                                                                                                                                                                                                                               |

| 0x17                             | Blue Gain LSB, (0x00)              | 5:0                  | N/A                                                                                        |                                                                                                                                                                                                                                                                                                            |

|                                  |                                    | 7:6                  | Blue Gain LSB                                                                              | See Red Gain                                                                                                                                                                                                                                                                                               |

| 0x18                             | Red Offset MSB, (0x80)             | 7:0                  | Red Offset MSB                                                                             | ABLC off: upper 8 bits to Red offset DAC ABLC enabled: Red digital offset 0x00 00 = min DAC value or -0x80 digital offset 0x80 00 = mid DAC value or 0x00 digital offset, 0xFF C0 = max DAC value or +0x7F digital offset                                                                                  |

| 0x19                             | Red Offset LSB, (0x00)             | 5:0                  | N/A                                                                                        |                                                                                                                                                                                                                                                                                                            |

|                                  |                                    | 7:6                  | Red Offset LSB                                                                             | 2 LSBs of 10-bit offset word                                                                                                                                                                                                                                                                               |

| ADDRESS | REGISTER<br>(DEFAULT VALUE)                    | BITS | FUNCTION NAME                            | DESCRIPTION                                                                                                                                                              |

|---------|------------------------------------------------|------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x1A    | Green Offset MSB, (0x80)                       | 7:0  | Green Offset MSB                         | ABLC off: upper 8 bits to Green offset DAC<br>ABLC enabled: Green digital offset<br>(See Red Offset)                                                                     |

| 0x1B    | Green Offset LSB, (0x00)                       | 5:0  | N/A                                      |                                                                                                                                                                          |

|         |                                                | 7:6  | Green Offset LSB                         | See Red Offset                                                                                                                                                           |

| 0x1C    | Blue Offset MSB, (0x80)                        | 7:0  | Blue Offset MSB                          | ABLC off: upper 8 bits to Blue offset DAC ABLC enabled: Blue digital offset (See Red Offset)                                                                             |

| 0x1D    | Blue Offset LSB, (0x00)                        | 5:0  | N/A                                      |                                                                                                                                                                          |

|         |                                                | 7:6  | Blue Offset LSB                          | See Red Offset                                                                                                                                                           |

| 0x1E    | PLL HTOTAL MSB, (0x06)                         | 5:0  | PLL HTOTAL MSB                           | 14-bit HTOTAL PLL updated on LSB write only.                                                                                                                             |

| 0x1F    | PLL HTOTAL LSB, (0x98)                         | 7:0  | PLL HTOTAL LSB                           | PLL updated on LSB write only. SXGA default                                                                                                                              |

| 0x20    | PLL Phase, (0x00)                              | 5:0  | PLL Sampling Phase                       | Used to control the phase of the ADC's sample point relative to the period of a pixel. Adjust to obtain optimum image quality One step = 5.625° (1.56% of pixel period). |

| 0x21    | PLL Pre-coast, (0x04)                          | 7:0  | Pre-coast                                | Number of lines the PLL will coast prior to the start of VSYNC                                                                                                           |

| 0x22    | PLL Post-coast, (0x04)                         | 7:0  | Post-coast                               | Number of lines the PLL will coast after the end of VSYNC.                                                                                                               |

| 0x23    | PLL Misc, (0x00)                               | 0    | PLL Lock Edge HSYNC                      | O: PLL locks to trailing edge of selected HSYNC (default)     1: PLL locks to leading edge of selected HSYNC                                                             |

|         |                                                | 1    | CLKINV ENABLE                            | 0: CLKINV input ignored 1: CLKINV input enabled                                                                                                                          |

|         |                                                | 2    | Ext Coast SEL                            | 0: Internal COAST generation 1: External COAST source                                                                                                                    |

|         |                                                | 3    | Ext Coast POL                            | 0: Active high external COAST 1: Active low external COAST                                                                                                               |

|         |                                                | 4    | EXT CLOCK                                | O: Internal pixel clock from DPLL     External pixel clock from EXTCLKin pin                                                                                             |

| 0x24    | DC-Restore and ABLC starting pixel MSB, (0x00) | 5:0  | DC-Restore and ABLC starting pixel (MSB) | Pixel after Raw HSYNC trailing edge to begin DC-restore an ABLC. 14 bits.                                                                                                |

| 0x25    | DC-Restore and ABLC starting pixel LSB, (0x02) | 7:0  | DC-Restore and ABLC starting pixel (LSB) |                                                                                                                                                                          |

| 0x26    | DC-Restore Clamp Width, (0x10)                 | 7:0  | DC-Restore clamp width                   | Only applies to DC-restore clamp used for AC-coupled configurations. A value of 0x00 means the clamp DAC is never connected to the input.                                |

| ADDRESS | REGISTER<br>(DEFAULT VALUE) | BITS | FUNCTION NAME                            | DESCRIPTION                                                                                                                                                                                                                                                                             |

|---------|-----------------------------|------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x27    | ABLC Configuration, (0x40)  | 0    | ABLC Disable                             | 0: ABLC on (default) - use 8-bit digital offset control. 0x000 = -0x200 LSB offset, 0x3FF = +0x1FF LSB offset, 0x200 = 0x000 LSB offset.  1: ABLC off - use 8-bit offset DACs, bypass digital adder (add/subtract nothing, but keep same delay through channel).                        |

|         |                             | 1    | Offset DAC Range                         | 0: ±1/2 ADC fullscale (1 LSB = 0.25 ADC LSBs)<br>1: ±1/4 ADC fullscale (1 LSB = 0.165 ADC LSBs)                                                                                                                                                                                         |

|         |                             | 3:2  | ABLC Pixel Width                         | Number of black pixels averaged every line for ABLC function 00: 16 pixels [default] 01: 32 pixels 10: 64 pixels 11: 128 pixels                                                                                                                                                         |

|         |                             | 6:4  | ABLC Bandwidth                           | ABLC Time constant (lines) = 2 <sup>([5+6:4])</sup> 000 = 32 lines 100 = 512 lines (default) 111 = 4096 lines                                                                                                                                                                           |

| 0x28    | Output Format 1, (0x00)     | 0    | Data Output Format                       | 0: 4:4:4 (24-bit output)<br>1: 4:2:2 (16-bit output on G and R)                                                                                                                                                                                                                         |

|         |                             | 1    | 4:2:2 Order                              | 0: First pixel on R channel is U 1: First pixel on R channel is V                                                                                                                                                                                                                       |

|         |                             | 2    | 4:2:2 Processing                         | 0: U, V filtered (high quality) 1: Odd U, V pixels dropped (lower quality)                                                                                                                                                                                                              |

|         |                             | 3    | 8-bit Mode                               | Should be set to 1                                                                                                                                                                                                                                                                      |

|         |                             | 5:4  | Oversampling                             | 00: Normal operation (1x sampling) 01:2x oversampling, 2 samples averaged at ADC output 10:4x oversampling, 4 samples averaged at ADC output 11:8x oversampling, 8 samples averaged at ADC output                                                                                       |

|         |                             |      |                                          | In Oversampling mode, the HTOTAL, DC-Restore/ABLC Start, DC-Restore Width, and ABLC width values are automatically multiplied by the oversampling ratio. The pixel clock is divided by the oversampling ratio when the data is decimated. Decimator is reset on trailing edge of HSYNC. |

|         |                             | 6    | RGB2YUV Color Space<br>Conversion Enable | 0: CSC Disabled 1: CSC Enabled Note: The data delay through the entire AFE is identical with CSC on and CSC off.                                                                                                                                                                        |

| ADDRESS | REGISTER<br>(DEFAULT VALUE)                                                         | BITS | FUNCTION NAME         | DESCRIPTION                                                                                                                                                                                                                                                                                                   |

|---------|-------------------------------------------------------------------------------------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x29    | Output Format 2, (0x00)                                                             | 0    | DATACLK Polarity      | D: Pixel data changes on falling edge (default)     Pixel data changes on rising edge                                                                                                                                                                                                                         |

|         |                                                                                     | 1    | FIELD output polarity | 0: Odd = low, Even = high (default) 1: Odd = high, Even = low                                                                                                                                                                                                                                                 |

|         |                                                                                     | 2    | Macrovision           | O: Digitize Macrovision encoded signals (default)  1: Blank AFE output for Macrovision encoded signals. If Macrovision is detected, AFE output is always 0x00, 0x00  0x00 for RGB, or 0x00, 0x80, 0x80 for YUV.                                                                                               |

|         |                                                                                     | 3    | HSOUT Polarity        | 0: Active High (default) 1: Active Low                                                                                                                                                                                                                                                                        |

|         |                                                                                     | 4    | HSOUT Lock Edge       | O: HSOUT's leading edge is locked to selected HSYNC <sub>IN</sub> 's lock edge. Trailing edge moves forward in time as HSOU width is increased (default).      HSOUT's trailing edge is locked to selected HSYNC <sub>IN</sub> 's lock edge. Leading edge moves backward in time as HSOUT width is increased. |

|         |                                                                                     | 5    | XTALCLKOUT Frequency  | 0: XTALCLKOUT = f <sub>CRYSTAL</sub> (default)<br>1: XTALCLKOUT = f <sub>CRYSTAL</sub> /2                                                                                                                                                                                                                     |

|         |                                                                                     | 6    | Enable XTALCLKOUT     | 0 = XTALCLKOUT is logic low (default)<br>1 = XTALCLKOUT enabled                                                                                                                                                                                                                                               |

| 0x2A    | HSOUT Width, (0x10)                                                                 |      | HSOUT Width           | HSOUT Width in pixels, 0x00 to 0xFF. HSOUT Lock Edge determines whether leading or trailing edge is locked to HSYNCin.                                                                                                                                                                                        |

| 0x2B    | Output Signal Disable,<br>(0xFF)                                                    | 0    | Tri-state Red         | 0 = Outputs enabled<br>1 = Outputs in tri-state                                                                                                                                                                                                                                                               |